具有额外电压输出能力的完整4 mA至20 mA HART解决

均有一个相应的CHARTx引脚, 因此HART信号可以耦合至AD5755-1的电流输出端。

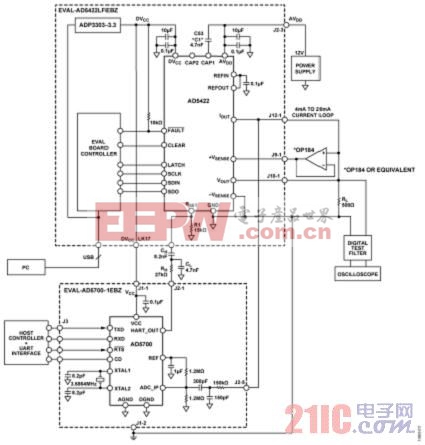

电路评估与测试

要构建此电路, 需要使用 AD5422评估板 ( EVAL-AD5422EBZLFCSP P版本)和 AD5700-1评估板 (EVAL-AD5700-1EBZ)1EBZ),参见图11。除了这两个评估板之外,该电路还需要三个外部电容(C1、CH和CL)、一个电阻(RH)、一个负载电阻(RL)、一个缓冲放大器以及一个UART接口。

设备要求 需要以下设备:

· AD5422 评估板( EVAL-AD5422EBZ LFCSP版本)

· AD5700 评估板( EVAL-AD5700-1EBZ)

· 运行Windows® XP的PC,带USB端口

· 主机控制器和UART接口(标准微控制器, 例如 ADuC7060)

· 10.8 V至60 V的电源

· 数字测试滤波器(HCF_TOOL-31,可从HART通信基金会获得)

· 500Ω负载电阻

· OP184 放大器(位于单独的试验板上且带有连接线)

· 外部电容C1 (4.7 nF)、CH (8.2 nF)和CL (4.7 nF);电阻RH (27 kΩ)

· Tektronix DS1012B示波器或等同产品

图11. 测试设置框图

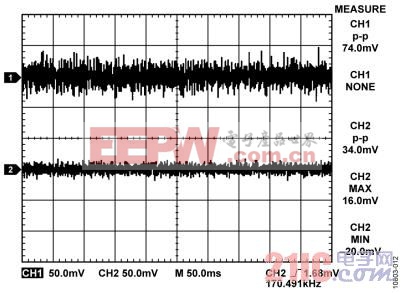

静默期间噪声测量 AD5422 LFCSP

如前文所述,对于静默测试期间的输出噪声,AD5700调制解调器并未在发射数据(静默)。AD5422设置为输出所需的电流并通过HART通信基金会带通滤波器。接着使用Tektronix TDS1012B示波器测量输出噪声;结果显示输出噪声在HART通信基金会协议规范要求的范围内。

模拟变化率测量 — AD5422 LFCSP

模拟变化率规范可确保当AD5422调节电流时,模拟电流的最大变化率不会干扰HART通信。电流的阶跃变化会扰乱HART信号。为进行这个测试,AD5422被编程为输出一个4 mA至20 mA切换的周期波形,该波形在两个值上都没有延迟,以获得最大变化率。所用的压摆率设置为SR时钟= 3和SR阶跃= 2,C1设置为4.7 nF,C2保持开路。

此外,再将SR时钟设置改变为5而不是3,并保持其它所有设置和元件值不变,从而进一步降低压摆率,由此另外进行测量;至于相关影响,可比较图9和图10来得出。

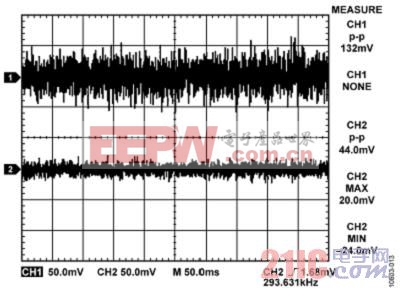

静默期间噪声测量 —AD5422 TSSOP

另外还执行了额外测量,以模拟AD5422 TSSOP封装选项在这种配置下的表现;不过,没有连接在CAP1引脚的电容(C1)(因为此器件的TSSOP版本没有CAP1引脚)。

虽然与有C1的LFCSP器件相比,没有C1时测得的静默期间输出噪声值更大,但还是在HART通信基金会协议规范要求的范围内。图12和图13中的通道2显示了有HCF_TOOL-31滤波器时的宽带噪声,IOUT为4 mA时结果为530μV rms,IOUT为12 mA时结果为690μV rms。可将这些曲线图与图7及图8进行比较,以体现有无C1的影响如何。

图12. 无C1且输出电流为4 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

图13. 无C1且输出电流为12 mA时HART滤波器输入(通道1)和输出(通道2)端的噪声

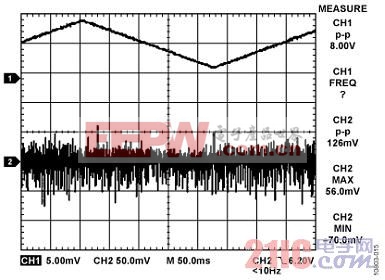

模拟变化率测量 — AD5422 TSSOP

从模拟变化率测试的角度来看,无论有无C1,最大峰值结果都相似。主要区别在于,没有C1时,峰峰值本底噪声要大得多。图14和图15分别是压摆率为120 ms(SR时钟= 3和SR阶跃= 2)和240 ms(SR时钟= 5和SR阶跃= 2)时的模拟变化率曲线图。

图14. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 3,SR阶跃= 2,C1 = NC,C2 = NC

图15. AD5422输出(通道1)和HART滤波器输出(通道2),SR时钟= 5,SR阶跃= 2,C1 = NC,C2 = NC

同样,可将这些曲线图与图9及图10进行比较,以体现有无C1的影响如何。虽然这种电路配置中所用的HART耦合技术要求采用外部RSET电阻,但请注意,即使该电路的HART部分未实施,添加缓冲器也会在使用内部RSET电阻时造成IOUT精度略微降低。因此,在使用这种缓冲器配置将电压和电流输出引脚连接在一起时,建议使用外部RSET电阻。

- HK模块在两线制以及HART隔离传输中的应用(01-21)

- 具有额外电压输出能力的完整4 mA至20 mA HART解决方案(10-16)

- ADI实验室电路:完整的HART兼容型4mA至20mA解决方案(一)(12-14)

- 完整的4mA至20mA HART解决方案(08-23)

- 不需要耦合电感器的 Hartley 振荡器(05-30)

- DS8500 HART调制解调器(10-25)