短波信道模拟器中数字下变频的设计

即完成频谱搬移。

2. 2 CIC 滤波器设计

CIC 积分梳状滤波器是实现高速抽取非常有效的单元。CIC 滤波器的单位冲激响应为:

从式( 2) 可以看出CIC 滤波器由2 部分组成,即积分器和梳状器级联组成,其实现非常简单,只有加减运算,没有乘法运算,FPGA 实现时可达到很高的处理速率。但是,单级CIC 滤波器的旁瓣电平只比主瓣低13. 46 dB,这就意味着阻带衰减很差,一般是难以满足实用要求的。为了降低旁瓣电平,可以采取多级CIC 滤波器级联的办法解决。

N 级CIC 滤波器级联的带内容差是单级CIC 滤波器带内容差的N 倍,这意味着多级CIC 滤波器级联增大阻带衰减的同时也增大了带内容差。所以,CIC 滤波器的级联数是有限的不宜超过5 级。

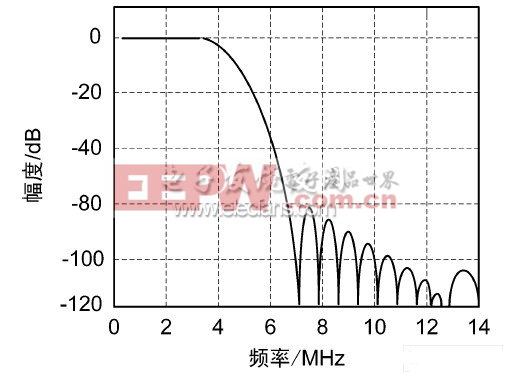

该设计中,CIC 滤波器需要完成16 倍的抽取,采用5 级级联来实现,输入和输出部分的位宽均为12 bit,在MATLAB 仿真的结果如图3 所示。

图3 CIC 滤波器幅度特性

经过CIC 滤波器后,信号采样速率经过16 倍抽取后变为4 MHz,从而实现了抽取功能,同时也降低了采样速率。

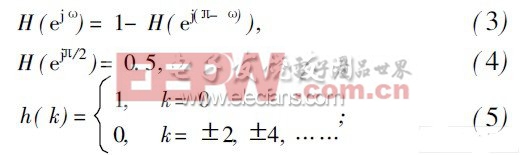

2. 3 半带滤波器

所谓半带滤波器,就是其频率响应满足以下关系的FIR 滤波器:

HB 滤波器由于其系数几乎一半为0,滤波时运算量减少一半,因此被作为第2 级低通滤波和抽取。

HB 的抽取因子固定为2,特别适合采样率降低一半的要求。通过CIC 和HB 滤波抽取后,基带信号由最初的高数据率被降到较低的速率,适于后级FIR处理。

2. 4 FIR低通滤波器设计

数字下变频器的最后一个模块是低通FIR 滤波器,主要用来对信号进行整形滤波不作抽取功能。

信号经过CIC、HB 滤波器后,输入到FIR 滤波器的采样速率相对来说已经很低,因此在一定的处理时钟速率下,能够有较高阶的FIR 滤波,使得滤波器的通带波动、过渡带带宽、阻带最小衰减等指标能够设计的很好。

调用MATLAB 的Filter design 获得滤波器的系数。在MATLAB 中设计一个通带截止频率为2 MHz的FIR,并将滤波器系数导入到FPGA 的FIR 中; FIR的阶数( 系数长度) 越高,性能越好,但考虑资源占用情况,FIR 的阶数不宜过高,该设计采用37 阶FIR。

3 基于FPGA 的DDC 系统仿真结果

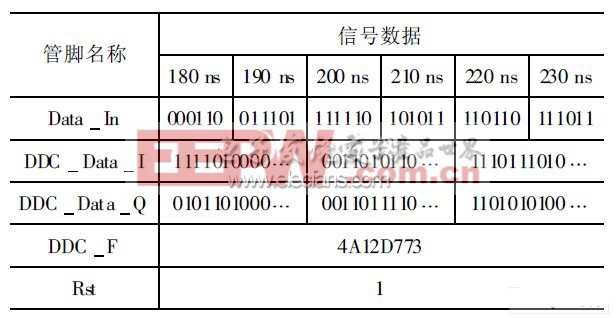

根据以上的设计分析结果,编写了FPGA 程序,在Quartus II 平台上进行了仿真测试。输入采样速率为64 MHz 的短波调制信号,针对Cyclone III 系列的EP3C40Q240C8 器件对其进行综合与时序仿真,如表1 所示。

表1 DDC 实现的时序仿真图

输入信号经过混频器后,再经过CIC 滤波器的16 倍抽取,半带滤波器的2 倍抽取和FIR 滤波器的整形滤波,最终输出I,Q 两路正交的信号。如表1所示,Data In 为输入信号,DDC Data I 为输出同相分量,DDC Data Q 为输出正交分量。64MHz 的采样信号经过NCO 混频后,CIC 滤波器的16 倍和HB 滤波器的2 倍抽取后,变为2 MHz 的信号,并经过FIR 滤波器整形输出。从表1 中可以看出设计的DDC 对于高速采样的信号具有降速和下变频的作用,处理带宽大大减小,因此对后续器件处理速度的要求降低。

仿真中还有一定量的毛刺,这是由于信号的延时控制不精准造成的。延时的大小不仅和连线的长短和逻辑单元的数目有关,而且也和器件的制造工艺和工作环境等有关,毛刺的消除是有待解决的问题。

4 结束语

在分析了宽带短波信道模拟器工作机理和数字下变频原理的基础上,结合Matlab 算法仿 真技术,设计基于FPGA 的数字下变频。功能与时序仿真结果表明: 基于FPGA 设计实现的数字下变频功能,其技术指标满足宽带短波信道模拟器的性能要求。该设计方法降低了对FPGA IP 核的依赖性,提高了DDC的处理速率,实现了数字载波控制和抽取滤波可编程,具有很大的灵活性和通用性,对于实现宽带短波信道模拟器具有十分重要的意义,并且可以推广用于其他需要进行下变频的场合。

- 宽带短波信道模拟器中数字下变频的实现(03-08)

- 单收/单发RS-232接口芯片 ADM101E及其应用(01-25)

- 设计高性能、低成本的笔记本电脑处理器电源 (05-12)

- 数字式光伏阵列模拟器的设计研究(02-25)

- 基于CAN总线的A320模拟器硬件仿真方案研究(03-21)

- 高性能模拟器件兼顾医疗设备诊断级精度和便携化需求(04-26)