Thunderbolt超高速I/O传输接口的ESD防护方案

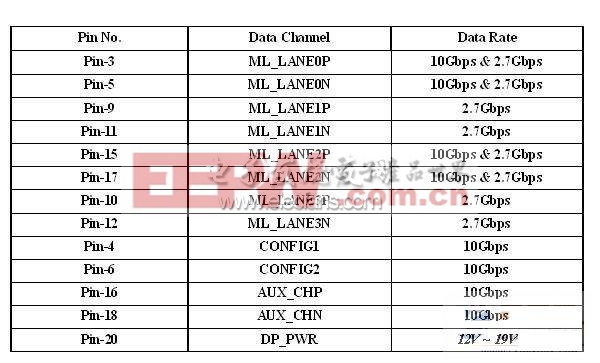

Thunderbolt技术以1颗桥接PCIe以及视讯整合的晶片,能够在3公尺的线长内传输达10Gbps的资料以及10瓦的供电,来作为界面控制,而接口在目前是先以铜缆来实现。在Intel与Apple的密切合作下,迅速地实际应用在Mac系列的产品上,以提供快速的资料传输服务。目前在Mac系列上的Thunderbolt是建构在mini-DisplayPort的实体接口上,其每条讯号线的传输速度规格如表1所示。而由于Thunderbolt是超高速的传输接口,在系统上属于外露给使用者可以插拔的接口,必然是静电放电(ESD)破坏的高风险区,因此ESD防护方案在此是绝对必要的。

表1,讯号线传输速度规格表。

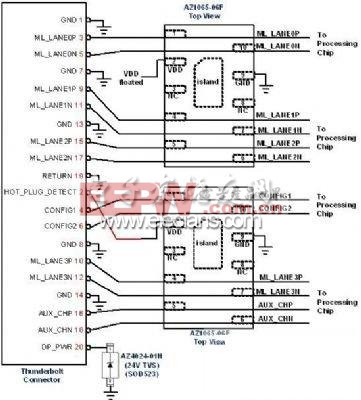

图1,Thunderbolt完整的接口接线图。

在设计Thunderbolt接口的ESD防护方案时,因为这个界面同时具备有数位影像以及数据传输的能力,因此在额外加入的ESD防护元件设计时,必须特别注意不可以影响到其超高速讯号的传输品质,为此晶焱科技特别设计了1颗ESD防护IC:AZ1065-06F,其每1根I/O接脚的寄生电容仅有0.27pF,可避免影响到高达10Gbps的讯号传输品质,而1个Thunderbolt接口仅需要2颗AZ1065-06F再加1颗AZ4024-01H就可以完整地保护此接口不受ESD的威胁,图1即为完整的接口接线图。

因为Thunderbolt接口的传输速率高达10Gbps,在设计ESD防护方案时,除了要尽量降低ESD防护元件接脚的寄生电容外,还必须维持PCB绕线(traces)的差动阻抗(differential impedance)不受影响,所以AZ1065-06F在设计时,还必须特别将其package接脚的空间间隔做特别设计,以符合维持PCB traces的differential impedance不会因为加上了AZ1065-06F而有所改变,图2即为AZ1065-06F实际的PCB布局(layout)范例。

在ESD防护IC的接脚之寄生电容与空间间隔,符合了不影响讯号传输品质的要求后,接着就要检视ESD防护IC所能提供的ESD防护效果。AZ1065-06F的每1根接脚对地,都被设计成可以承受IEC61000-4-2 contact mode 8KV以上的ESD轰击,且其所提供的箝制电压(Clamping Voltage)在6KV时仅有13V而已。因此AZ1065-06F除了本身的ESD防护性能力外,更结合了如图1和图2的接线与PCB layout设计,使得Thunderbolt接口可以承受高达8KV的ESD轰击,而不会有受到破坏的危险状况发生。这样的设计可以大大地降低Thunderbolt接口因ESD轰击而失效的机率,也是现今高速电子产品迫切需要的防护设计,因为这类高速接口对应的主要传输晶片,都是采用最先进的半导体制程所设计,这类先进制程的高速晶片本身对ESD耐受能力极为薄弱,所以非常仰赖接口的ESD防护方案。

Thunderbolt 超高速 I O传输 ESD防护 相关文章:

- Thunderbolt? 2 如何实现 4k 视频分辨率(06-25)

- 关于Thunderbolt接口你应该知道的事(09-23)

- Thunderbolt是什么(04-12)

- Thunderbolt/IEEE 1394/e-SATA/USB3.0接口对比(04-12)

- 微电子所在超高速ADC/DAC芯片研制方面取得突破性(10-09)

- 超高速模数转换器(12-14)