增益增强共源共栅放大器的设计

模负反馈结构,这种结构会限制放大器输出摆幅,但却不会影响放大器增益,并且功耗较低,因此适合用于辅助放大器中。共模负反馈电路如图5所示。

1.4 偏置电路

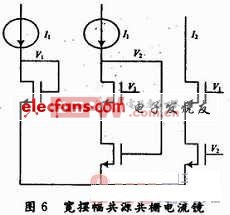

由于整个电路中有许多共源共栅管需要提供偏压,因此采用了共源共栅宽摆幅电流镜来对这些管子提供偏置,宽摆幅共源共栅电流镜在保证电流复制精度的同时提高了摆幅,使得电路在保证输出摆幅的同时保持正常工作。宽摆幅共源共栅电流镜电路图如图6所示,其中I2=I1。

2 电路仿真结果

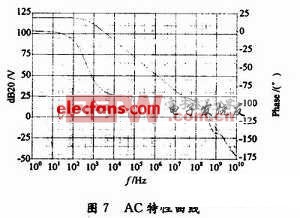

整个运放及其偏置电路采用SMIC 0.18μmCMOS混合信号工艺进行设计,并在Cadence环境下用Specture进行模拟仿真,电源电压3.3V,负载电容3 pF。对电路进行AC仿真,仿真结果显示电路直流增益119.3 dB,单位增益带宽378.1 MHz,相位裕度60°,如图7所示。

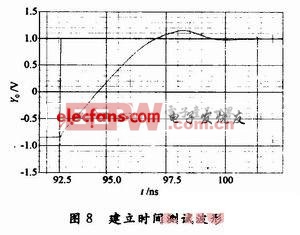

放大器建立到输出电压0.1%精度时的建立时间为7.9 ns,测试波形如图8所示。

共模输入范围600mV~3.3V;电压输出范围0.6~3.1V;功耗39mW。

3 版图设计

整体电路包括1个主放大器,2个gainboost和1个共模负反馈,主放大器和gainboost各有自己的偏置电路。gainboost的偏置电路和gai-nboost放大器靠近放置以使连线最短,2个gainboot分别放在主放大器两侧以使总体版图对称,开关电容共模负反馈放在主放大器下面以使out+,out-和Vb1连线最短。主放大器做ABAB匹配,采用双侧供电,以保证差模信号较好匹配,主放大器偏置分拆在主放大器两侧,以使总体版图形状更加规则整齐,节省面积。

4 结语

介绍了一种折叠式共源共栅运算放大器的设计。实际的设计仿真值为:小信号低频电压增益119.3 dB;单位增益带宽378.1 MHz;相位裕度60°;建立时间7.9 ns;电源电压3.3 V;共模输入范围600 mV~3.3 V;电压输出范围0.6~3.1 V;负载电容3 pF;功耗为39 mW。整个设计满足设计指标要求,并应用于欠采样技术的12 b,60 MHz流水线ADC设计中。

- 一种改进的增益增强共源共栅放大器的设计(07-12)

- 高增益三级比较器设计与仿真研究(08-13)

- RFC电路设计及分析(02-08)

- 一款高性能共源共栅运算放大器设计(05-22)

- 使用简化电路的高压放大器(11-21)

- 无需调谐的“砖墙式”低通音频滤波器(11-20)