基于DDS器件AD9858的复杂雷达信号源简介

摘 要:本文简要介绍DDS器件AD9858的系统结构和基本原理,以及使用AD9858实现复杂雷达信号源的原理和方法,并以AD9858产生二相码为例,说明了AD9858的基本特点和使用中应该注意的一些问题。

关键词:复杂雷达信号源;二相码;DDS;AD9858

引言

20世纪70年代以来,随着数字集成电路和微电子技术的发展,出现了DDS(直接数字式频率合成)技术,它从相位的概念出发进行频率合成,采用了数字采样存储技术,具有相位精确、频率分辨率高、转换时间短等突出的优点。高性能DDS技术结合DSP技术、大规模可编程逻辑器件技术使得实现线性调频相位编码混合信号成为可能。

AD9858简介

---AD9858的10位数摸转换器可工作到1GSPS,可产生400MHz的频率捷变模拟输出正弦波,具有快速调频和细微的频率分辨率(32位频率分辨率)。内部有集成的电荷泵(CP)和相频检测器(PFD),可以将高速DDS和锁相环(PLL)结合使用。片内模拟混频器又可使DDS、PLL和混频器结合使用。AD9858可对对输入时钟进行二分频,这样外部输入时钟可以高达2GHz。

---AD9858有三种工作模式:单音频、频率扫描和全睡眠模式,在任何一种模式下射频模块(PFD、CP、混频器)可以使用或不使用,可以处于活动或低功耗状态。单音频模式下,AD9858产生由内部寄存器FRW控制的单频输出信号。频率可以任意改变,频率跳变的速度与刷新相应寄存器的速度有关。假如想得到快速跳频,可以通过外部引脚来选择4个存储在寄存器中的频率值来实现。频率扫描模式可以自动完成频率扫描工作,产生线性调频或实现其他频率扫描应用,而且不受I/O口对多寄存器操作时的速度限制。AD9858有并行和串行两种编程模式,有4个相互独立的工作组(profile 0~3),每个工作组由32位的频率调制字(FTWx)和4个14位的相位补偿字(POWx)组成,4个工作组之间由外部引脚PS0和PS1进行切换,其对应关系如表1所示。

---无论AD9858工作于哪种工作模式,分别设定Profile工作组的FTWx和POWx,通过改变PS1和PS0的值,就可以同时改变信号的频率和相位,而且相位的改变可以是绝对调相或相对调相,这正是AD9858实现混合调制的关键。相对于较早前使用的DDS器件AD9854,AD9858大大缩短了码元间的转换时间。因为AD9854仅有一个相位补偿器(POW),这使得AD9854只有通过外部更新信号来改变相位补偿器的内容,以实现相位调制,所以AD9854码元转换时间较长。

---参数写入AD9858的寄存器后,只需产生PS0和PS1的控制时序就可以产生相应的二相码。例如用AD9858产生二相码时,首先通过并行模式或串行模式把频率和相位参数写入相应的FTWx和POWx,4个工作组中每2个工作组中的参数相同。这样通过选择PS0和PS1就可以输出二相码。

---值得注意的是,这里使用了4个工作组,其中2个工作组中的POW为0,另外2个工作组中的POW为π。当相邻的两个子码的相位相同时,可以将输出改为参数相同的另一个工作组进行输出,这样可以保证相位的准确性。如果只使用2个工作组来输出二相码,就需要用到外部更新信号FUD,通过外部控制器(如ADSP21065L)重新更新AD9858寄存器的内容,来保证相位的准确,这样不但增加了码元的转换时间,而且控制也会变得复杂。

硬件电路设计

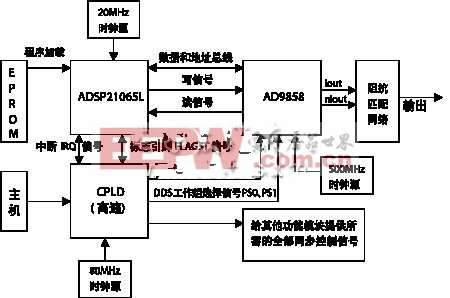

---线性调频相位编码混合调制信号源系统的框图如图1所示,主要由AD9858、DSP处理器ADSP21065L和CPLD构成。

---CPLD的作用是产生整个DDS系统需要的全部同步控制信号,接受主机提供的控制信号和波形参数选择信号,产生相应的ADSP21065L中断信号。ADSP21065L根据中断信号来确定雷达工作波形,产生相应工作参数,然后对AD9858进行相应的初始化和置数。CPLD还将波形参数、工作模式等信息通过I/O端口发送给雷达发射机、信号处理机等相应的其他处理单元。用CPLD来控制AD9858具有工作波形稳定、时序容易控制、精度高和后期调试简单的优点。AD9858是信号源的核心,在接收ADSP21065L的参数后,确定相应的工作状态,等待CPLD产生相应的控制信号,输出相应的波形。AD9858输出的信号经过阻抗匹配网络后,输出混合调制信号。

实验结果和结论

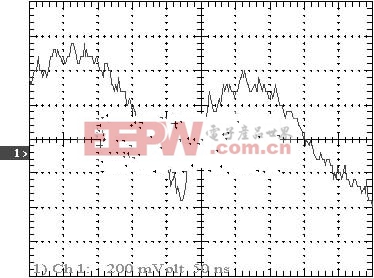

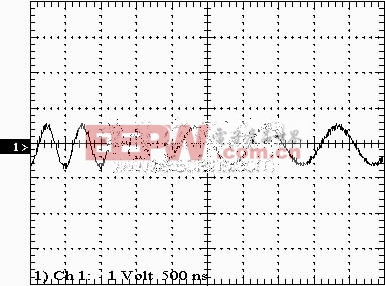

---在实际产生二相码的时候,由于通过外部引脚PS0和PS1的变化来改变二相码的子码转换,这个过程中不可避免地会使子码与子码之间有一定的转换时间,转换时间主要取决于AD9858的外部更新信号FUD。子码转换如图2所示,系统为40MHz时,子码1频率为2MHz、初相为0°,子码2频率为1MHz、相位为180°,图3是图2的局部放大示图。

---由图可见,子码1到子码2的码元转换时间约200ns,基本等于AD9858的FUD时间。如果将系统时钟提高到400~500MHz时,FUD的时间可以缩短到20ns以下。因此,可以通过提高系统时钟频率来减小子码

- 基于AD9858宽带雷达信号源的设计及应用(10-11)

- DDS器件AD9858实现复杂雷达信号源(08-29)

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)