LDO的工作原理详细分析二

时间:12-12

来源:互联网

点击:

一般为100mΩ-5Ω,只适合使用钽电容并不适合使用陶瓷电容。

要弄清ESR取之范围上限下降的原因,请参考图15。上文提到,此LDO的零点已被集成在IC内部。因此外部电容产生的零点必须处在足够高的频率,这样就不能使带宽很宽。否则,高频极点会产生很大的相移从而导致振荡。

使用场效益管(FET)作为导通管LDO的优点

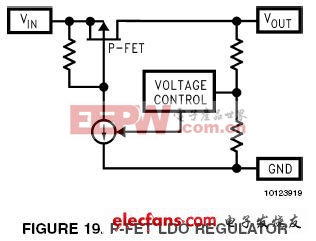

LDO稳压器可以使用P-FET(P沟道场效应管)作为导通管(图19:P沟道场效应管LDO内部结构框图)。为了阐述使用Pl-FET LDO 的好处,在PNP LDO(图2)中要驱动PNP功率管就需要基极电流。基极电流由地脚(ground pin)流出并反馈回反相输入电压端。因此,这些基极驱动电流并未用来驱动负载。它在LDO稳压器中耗损的功耗由下式计算:

PWR(Base Drive)=Vin × Ibase (11)

图19

需要驱动PNP管的基极电流等于负载电流除以β值(PNP管的增益)。在一些PNP LDO稳压器中β值一般为15~20(与负载电流相关)。此基极驱动电流产生的功耗可不是我们期望的(尤其是在电池供电的低功耗应用中)。P沟道场效应管(P-FET)的栅极驱动电流极小,较好地解决这个问题。

P-FET LDO稳压器的另一个优点,是通过调整场效应管(FET)的导通阻抗(ON-resistance)可以使稳压器的跌落电压更低。 对于集成的稳压器而言,在单位面积上制造的场效应功率管(FET power transistors)的导通阻抗会比双极型开关管(Bipolar ONP Devices)的导通阻抗低。这就可以在更小封装(Packages)下输出更大的电流。

- 如何设计一个合适的系统电源(上)(11-20)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 用低压差线性稳压器优化开关电源设计(01-18)

- LDO稳压器等效串联电阻的稳定范围(01-24)

- 低电压PLD/FPGA的供电设计(01-24)

- 拥有线性稳压器特性的下一代移动DC-to-DC转换器(02-08)