在FPGA上建立MATLAB和Simulink算法原型

。

HDL仿真仅提供数字波形输出,而HDL协同仿真则提供了显示HDL代码的完整视图,并可以访问Simulink的全套系统级分析工具。当工程师观察到预期结果与HDL仿真结果存在差异时,可借助协同仿真进一步了解该失配所产生的系统级影响。

例如,在图9中,频谱仪视图可以使工程师做出明智决定,忽略预期结果与HDL仿真结果之间的失配,其原因是该差异位于阻带区。相比之下,数字波形输出只是将预期结果与HDL仿真结果的失配标记为误差。尽管工程师最终可能得出相同的结论,但这将需要更多的时间完成所需的分析。

测试覆盖率:工程师可以使用HDL验证工具、Simulink设计验证工具和ModelSim/Questa自动执行代码覆盖率分析。在该工作流程中,Simulink设计验证工具可针对模型覆盖率生成一套测试用例。HDL验证工具自动使用这一套测试用例运行ModelSim/Questa,收集代码覆盖率数据,以对生成的代码加以全面分析。

使用FPGA在环仿真加速验证

使用系统级仿真和HDL协同仿真验证DDC算法之后,便可以立即在FPGA目标平台上部署DDC算法。对算法执行基于FPGA的验证(也称为FPGA在环仿真)可以增强对算法在现实环境中有效运行的信心。相比基于主机的HDL仿真,该验证可以使工程师更快地运行测试方案。

对于DDC算法而言,可以使用Simulink模型驱动FPGA输入激励并分析FPGA的输出(图10)。与HDL协同仿真一样,在Simulink中始终可以利用相关数据进行分析。

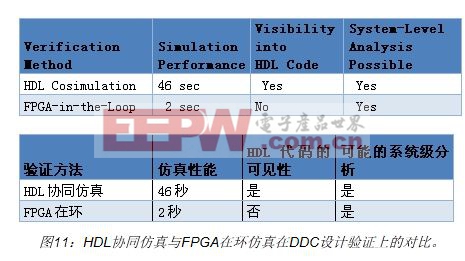

图11对比了HDL协同仿真和FPGA在环仿真这两种用于DDC设计的验证方法。在本案例中,FPGA在环仿真的速度是HDL协同仿真的23倍。这样的速度提升使工程师能够运行更广泛的测试用例并对其设计进行回归测试。这使他们能够识别出有待进一步分析的潜在问题区域。

尽管HDL协同仿真速度较慢,但它却提高了HDL代码的可见性。因此,它很适合针对FPGA在环仿真过程中发现的问题区域进行更详细的分析。

本文小结

如果工程师遵循本文所述的四种最佳方法,开发FPGA原型将比传统的手动工作流程快出许多,并能使工程师信心倍增。此外,工程师还可以在整个开发过程中继续优化自己的模型,并快速地重新生成有关FPGA实现的代码。与依赖手工编写HDL的传统工作流程相比,这种能力可以显着缩短设计迭代的周期。

- 基于Simulink技术的噪声调幅干扰仿真(03-08)

- PWM整流器在电动汽车充电机上的应用(02-04)

- 一种用于压力传感器的温度控制系统设计(02-10)

- 基于Matlab/Simulink的变频系统仿真(08-23)

- 电力驱动系统逆变器实时仿真(08-16)

- 基于MEMS的无线鼠标设计方案(12-01)