高介电常数栅电介质/金属栅极的FA CMP技术

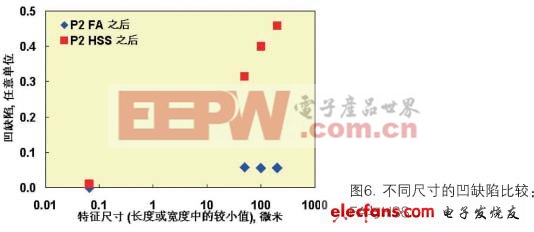

HSS工艺在不同特征尺寸下的凹缺陷表现。当特征尺寸达到50微米时,凹缺陷的表现就会有明显差异。FA优异的凹缺陷表现使其成为RMG ILD0化学机械研磨工艺的关键步骤。

P2对于P3工艺的影响

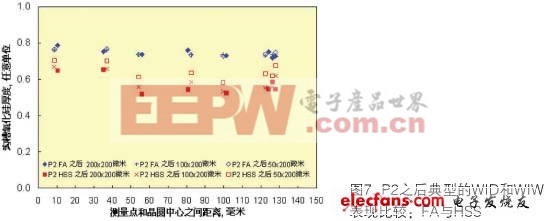

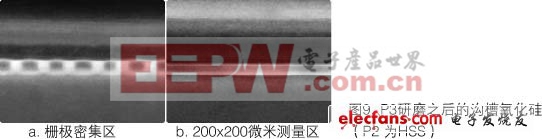

图8-11中,所有SEM照片的拍摄角度均为45度。晶圆纵切面通过FIB切割方式获得。所有的照片使用相同的比例尺。图8比较了P2用HSS工艺研磨后的栅极密集区和200×200微米测量点的沟槽氧化硅厚度。栅极密集区和大尺寸测量区的厚度明显不同,表明存在显著的WID差异。P3的无选择性研磨浆工艺将很难修复P2造成的WID差异。如图9所示,如果P2使用HSS工艺,栅极密集区和大尺寸测量区的沟槽氧化硅厚度差异在P3之后仍然会很高。

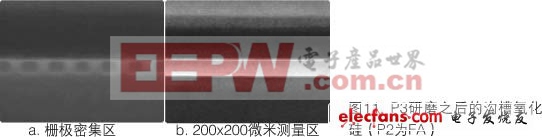

相对于HSS,FA研磨后的WID厚度差很小。图10显示沟槽氧化硅在密集区和大尺寸测量区的厚度非常接近。这种低WID差异会被进一步保留至无选择性的P3之后(图11)。上述对比显示,FA有能力解决线路密度和尺寸不同造成的平坦度挑战,从而减少芯片设计规则中对于线路密度的限制。

用FullVision控制多晶硅厚度

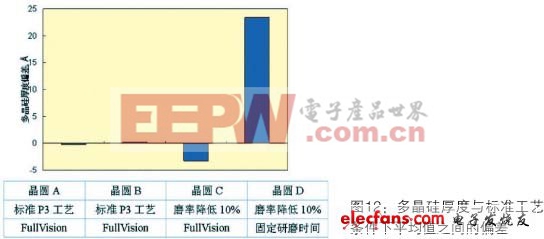

持续稳定的多晶硅厚度控制是通过FullVision实时终点控制系统来实现的。该系统的可靠性和可重复性已在实际生产中得到证明。图12显示出FullVision终点控制系统的强大功能。在图12中,晶圆A和B都使用标准P3工艺研磨,并利用FullVision控制研磨终点;晶圆C和D的P3磨率低于标准磨率10%;晶圆C通过FullVision控制研磨终点,而晶圆D的研磨时间与晶圆A和B的研磨时间相同。上述四片晶圆的P1和P2研磨条件完全相同。

FullVision自动调整晶圆C的研磨时间来补偿P3磨率的下降。因此,晶圆A、B和C在P3之后的栅极多晶硅厚度差异小于5?。由于晶圆D没有使用FullVision终点侦测控制系统,而是使用与晶圆A相同的研磨时间进行研磨,因此晶圆D在P3之后的栅极多晶硅厚度与标准工艺条件的平均厚度相差高达25?。

使用无选择性的P3研磨浆会使工艺本身对P3磨率随研磨垫寿命的偏移以及上游步骤工艺的变化(比如氮化硅厚度改变,P2过度研磨程度等)非常敏感。FullVision可以通过自动调节研磨时间来应对生产过程中各种无法预测的偏移,从而确保稳定的WTW表现。

无论是在栅极密集区还是在大尺寸测量区,图13中的SEM纵切面图片都展示出均一的表面形貌。

结论

良好的WID、WIW和WTW厚度控制是制造基于HKMG技术的高性能逻辑芯片的关键。ILD0化学机械研磨工艺利用FA对不同尺寸大小和密度的芯片结构均提供优异的表面形貌和平坦度控制,并且通过使用FullVision实时终点控制系统进一步确保稳定的WTW厚度控制。

- 飞兆半导体交错式临界导通PFC控制器为绿色电源提供超过96%的效率(01-20)

- 光纤放大器( EDFA )的调试与维护(01-25)

- 飞兆半导体的栅极驱动器提高汽车应用的燃油效率(02-19)

- 飞兆半导体的TinyBuck 参考设计能够简化DC-DC转换设计(03-20)

- 智能交错—实现高效 AC/DC 电源的先进 PFC 控制器(08-18)

- 让高功率电源获得96%效率的交错式PFC控制器(01-08)