高介电常数栅电介质/金属栅极的FA CMP技术

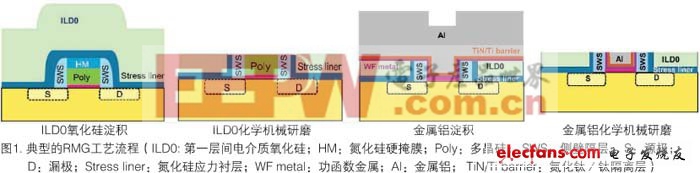

典型的RMG工艺流程依次包括(图1):临时多晶硅栅极结构的形成,第一层间电介质(ILD0)氧化硅的沉积,ILD0化学机械研磨直至临时多晶硅栅极完全曝露,刻蚀去除多晶硅栅极,功函数材料的淀积,金属铝的沉积,以及金属铝的化学机械研磨。作为RMG工艺流程步骤之一,ILD0化学机械研磨对于HKMG结构的顺利形成至关重要。

由于栅极结构对尺寸控制要求非常严格(WIW和WID),如果缺少严格控制最终研磨厚度的工艺手段,将会带来一系列的工艺整合问题,比如:栅极电阻波动,栅极填充不足,源/漏极曝露等等。这些问题最终都会损害芯片性能。为了确保芯片的优良性能和可靠性,制造工艺必须严格控制WIW、WID以及WTW的厚度差异。

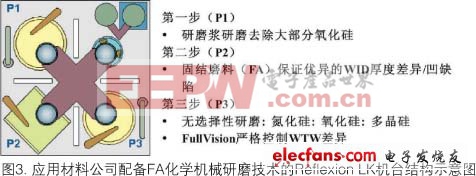

应用材料公司已经成功研发出一套在Reflexion? LK机台上实现的三步化学机械研磨工艺,以解决ILD0化学机械研磨过程中的WIW、WID和WTW厚度控制问题。第一步(P1),研磨移除大部分的ILD0电介质材料;第二步(P2),采用FA继续研磨,接触到栅极区域氮化硅层后停止;第三步(P3),栅极区域的氮化硅层被彻底磨掉,多晶硅栅极完全曝露。图2演示了在ILD0化学机械研磨过程中,沟槽区氧化硅研磨去除的全过程。

实验细节

应用材料公司的Reflexion? LK研磨机台包括一个FA研磨盘和两个标准的旋转式研磨浆研磨盘,使用可以控制5个独立区域压力的Titan ContourTM研磨头(图3)。FA研磨盘配有3M公司生产的SlurryFreeTM 固结磨料卷轴和SlurryFree P6900基底研磨垫。研磨浆研磨盘配有Dow Chemical公司生产的IC1010TM研磨垫和3M公司生产的研磨垫修复刷。P1使用Cabot公司生产的Semi-SperseR SS-12氧化硅研磨浆;P2使用FA研磨液;P3使用专用的研磨浆。

本文将统一使用一种简化的栅极结构(图4)以评估不同工艺的表现。栅极区域结构从上到下依次为:氧化硅/氮化硅/多晶硅/栅极氧化物/单晶硅,“沟槽”特指栅极与栅极之间的区域(结构为:氧化硅/单晶硅)。在尺寸大于50微米的测量区,薄膜厚度的测量使用Nanometrics公司的NanoTM 9010b。而对栅极尺寸小于100纳米的测量点,则需要通过扫描电子显微镜(SEM)进行纵切面观测。本文中,一部分样品通过机械劈裂的方式获得晶圆纵切面;另一部分样品使用聚焦离子束(FIB)局部切割晶圆露出纵切面。

结果与讨论

P3需要无选择性的研磨浆

因为P3之后的平坦度要求非常严格,P3的研磨倾向于使用无选择性研磨浆。该研磨浆在氮化硅、氧化硅和多晶硅上都有可观的磨率。首先,氮化硅的磨率必需足够高才能保证多晶硅栅极完全曝露。如果氧化硅的研磨率显著低于氮化硅和多晶硅,则可能导致沟槽区域明显凸起,并随着过度研磨而恶化。如果多晶硅的研磨率显著低于氮化硅和氧化硅,那么栅极和沟槽之间的高度差会对研磨不足或过度研磨非常敏感。使用无选择性的研磨浆将会减少由于P3研磨时间不同造成的栅极和沟槽之间的高度差变化。

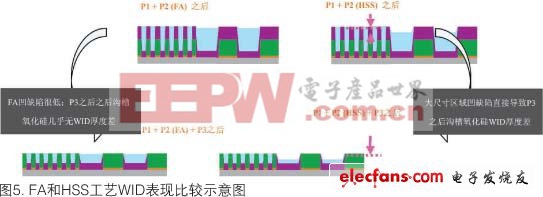

P2 FA工艺可以降低P3之后沟槽氧化硅的WID厚度差异

FA工艺已被广泛应用于直接研磨浅沟槽隔离(STI)。FA可以选择性的停在氮化硅表面,并展现出优异的研磨平坦度和低的凹缺陷。与STI类似,ILD0的研磨也包括停在氮化硅表面的步骤。这种极低氮化硅损失和极低氧化硅凹缺陷的工艺特点使得FA成为ILD0研磨工艺中WIW和WID厚度控制的关键。在栅极密集区,由于特征尺寸很小,不论使用FA工艺还是高选择性的研磨浆(HSS)研磨工艺,凹缺陷一般都比较低(图5)。然而在外围区域,特征尺寸可能达到50微米以上,HSS研磨工艺一般都会产生明显的凹缺陷(>200?),而FA研磨工艺仍能保持低凹缺陷(50?)。

因此,对比FA工艺和HSS工艺研磨后的沟槽氧化硅WID厚度差异,前者明显低于后者。由于P3使用无选择性的研磨浆,P2之后的高凹缺陷就会直接导致P3之后的沟槽氧化硅WID厚度差异也很高(图5)。从晶圆纵切面的SEM照片中可以清楚的看出P3之后的WID厚度差异。

FA优异的平坦度和凹缺陷表现

与HSS工艺相比,FA工艺能够明显降低沟槽氧化硅的WID厚度差异和凹缺陷,尤其在大特征尺寸区域。与此同时,FA过度研磨不会显著降低WIW和WID表现(图7)。图6对比了FA和

- 飞兆半导体交错式临界导通PFC控制器为绿色电源提供超过96%的效率(01-20)

- 光纤放大器( EDFA )的调试与维护(01-25)

- 飞兆半导体的栅极驱动器提高汽车应用的燃油效率(02-19)

- 飞兆半导体的TinyBuck 参考设计能够简化DC-DC转换设计(03-20)

- 智能交错—实现高效 AC/DC 电源的先进 PFC 控制器(08-18)

- 让高功率电源获得96%效率的交错式PFC控制器(01-08)