D类功放设计须知(四)

死区校正)

全桥MOSFET管轮流成对导通,理想状态一对导通,另一对截止,但实际上功率管的开启关断有一个过程。过渡过程中,必有一瞬间,如图3所示,在IN1/IN3尚未彻底关断时IN2/IN4就已开始导通;因MOSFET全部跨接于电源两端,故极端的时间内,可能会有很大的电压电流同时加在4个MOSFET上,导致功耗很大,整体效率下降,而且器件温升加剧,烧坏MOSFET,降低可靠性。为避免两对MOSFET同处导通状态,引起有潜在威胁的很大短路电流,应保证一对MOSFET导通和另一对MOSFET截止期间有一个很短的停滞死区时间(Dead-time),这个时间由Logic逻辑控制器控制,以有效保证一组MOSFET关断后,另一组MOSFET再适时开启,减小MOSFET损耗,提高放大器效率。

但Deadtime设置不当,将出现如下问题:

(1)输出信号中将产生毛刺,造成电磁干扰,也即死区时间内,IN1/IN3都关断。完全失控的输出电压将受到图6(a)中体二极管电流的影响(体二极管电流的形成,参见下文EMI节),输出波形中将出现毛刺干扰。

(2)Deadtime过大,输出波形中出现的毛刺包含的能量将持续消耗在体二极管中,以热能形式消耗能量,严重影响芯片工作稳定性和输出效率。

(3)Deadtime过长,影响放大器线性度,造成输出信号交越失真,时间越长,失真越严重。

2.2 EMI(Electro-Magnetic InteRFerence)

EMI主要由MOSFET体二极管反向恢复电荷形成,具体产生机理如图6所示。

第一阶段,MP1-MOSFET导通,有电流流过MOSFET和后级LPF电感;第二阶段,全桥进入Dead-time期间,MP1本身关断,但其体二极管依然导通,保证后级电感继续续流;第三阶段,Deadtime期结束,MN1导通瞬间,若MP1体二极管存储的剩余电荷尚未完全释放,则瞬间释放上一次导通期间未释放的存储电荷,导致反向恢复电流激增,此电流趋向于形成一个尖脉冲,最终体现在输出波形上,如图6(b)所示。因此,输出频谱会在开关频率以及开关频率倍频处包含大量频谱能量,对外形成EMI。

为抑制EMI,以降低输出方波频率,减缓方波顶部脉冲为目的,将一些内部EMI消除电路新技术应用于新产品中:

(1)Dither。扩展频谱技术,即在规定范围内,周期性调整三角波采样时钟频率,基波和高次谐波避开敏感频段,使输出频谱能量平坦分散;

(2)增加主动辐射限制电路,输出瞬变时,主动控制输出MOSFET栅极,以避免后级感性负载续流引起高频辐射。

2.3 印制板PCB布局设计规则

(1)因输出信号含大量高频方波,需将加入的低失真、低插入损耗LC滤波电容和铁氧体电感低通滤波器件紧密靠 近功放,将承载高频电流的环路面积减至最小,以降低瞬态EMI辐射。

(2)因输出电流大,音频输出线径要宽,线长要减短,故需降低无源电阻RP和滤波器电阻RF,提高负载电阻RL比值,提高输出效率。

(3)PCB底部是热阻最低的散热通道,功放底部裸露散热铜皮面积要大,应尽可能在敷铜块与临近具有等电势的引脚以及其他元件间多覆铜,裸露焊盘相接的敷铜块用多个过孔连接到PCB板背面其他敷铜块上,该敷铜块在满足系统信号走线要求下,应具有尽可能大的面积,以保证芯片内核通过这些热阻最低的敷铜区域有最佳散热特性。

(4)大电流器件接地端附近,多加过孔,信号若跨接于PCB两层间,多加过孔提高连接可靠性,降低导通阻抗。

(5)信号输入端元件焊盘和信号线与输出端保持适当间距,关键反馈网络器件置放在输入/输出PCB布局模块中间,防止输出端EMI幅射影响输入端小信号。

(6)地线、电源线远离输入/输出级,采用单点接地方法。

3 基于上述要素的绿色能效D类功放TFA9810T设计应用

3.1 TFA9810T内部结构

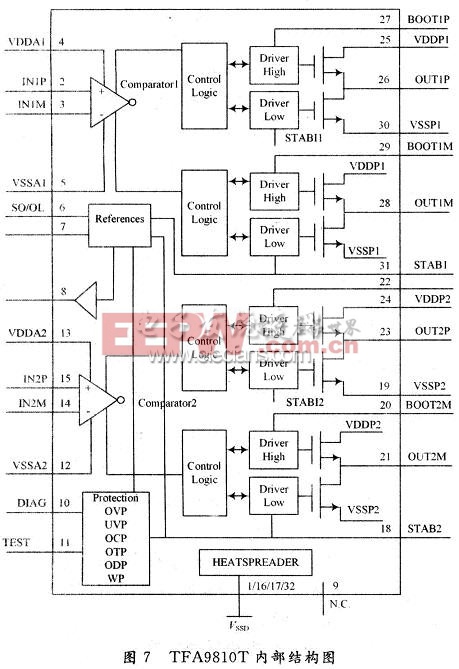

TFA9810T是NXP公司推出的双通道额定输出2×12 W的高效Class-D类功放,主要由两组全桥功率放大器(Full-Bridge)、驱动前端、逻辑控制、OVP/OCP/OTP等保护电路、全差分输入比较器、供电模块等构成,如图7所示。

其具备如下特点:可取消散热器,有很高的可靠性,8~20 V单电源供电,外部增益可调,待机节能状态的供电电流为微安级,耗能很小等。非常适合应用于平板类电视产品、多媒体系统、无线音频领域。

- 新型无滤波器D类放大器及其应用设计技巧 (01-09)

- D类放大器散热注意事项(01-19)

- D类放大器原理详解及应用设计指南(01-12)

- D类放大器原理详解及应用设计指南(二)(01-12)

- D 类提高音频放大器的效率(02-13)

- 改善平板显示器的音频性能(02-13)