在线测试技术的现状和发展(二)

首先,我们要回顾一下数字器件的特点,数字器件只有2种电平:高电平和低电平,所以测试程序要能定义逻辑电位,数字器件比模拟器件多很多管脚,因而测试仪不可能在管脚间不停地切换模拟源和测量仪表。因此,测试仪要有一套能驱动数字芯片输入端到理想电位的数字驱动器,也要有一组能检测其输出逻辑电位的数字感应器。

驱动器和感应器(Driver/Sensor)是成对存在的,驱动器的输出端总是与感应器的输入端相连,在程序控制下,同个测量节点在某个时候可能被驱动到某个电位,而另个时候,又有可能被感应器测量它的输出。

(1)驱动器/感应器的编程

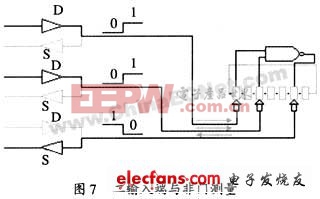

为了说明程序是怎样控制驱动器/感应器,让我们看一个简单的二输入与非门例子,如图7。

只有与非门输入端全为高电平时,输出端才为低电平,而其他状态的组合,输出端都为高,要对这个二输入与非门进行测量,测试程序应按以下工作:

1)给被测板上电、接地

2)定义高、低电平

3)指定测试针

4)定义驱动和感应测量时序

对上述单个与非门,测试程序将会检查所有4种输入的工作情况。

每一行程序语句代表一个测试矢量。IC、IH和IL连接驱动器到指定的输入端A和B,并给予赋制值;OS、OH和OL连感应测量端到输出端C,并告之期望值。所有驱动器和感应端值在程序命令改变之前保持不变。

(2)数字芯片的隔绝和测量

因为被测数字器件必须要上电才能测量,在板上器件间又存在连结,因此电源也会加到其他器件上,这样一来,当测试仪要给被测芯片的某输入端加驱动信号时(如高电平),此输入端可能被另一芯片的输出保持在相反电位(低电平)。

数字驱动器在瞬间强制被测芯片的输出端到指定电平,而不管其他芯 片影响,来解决这个问题,这种技术称背驱动技术。

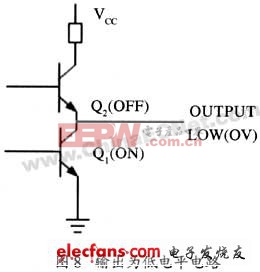

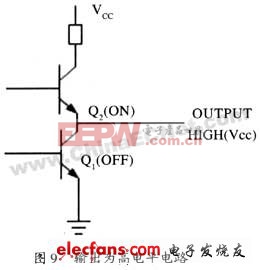

考虑一个典型的TTL芯片输出状态,如图8、9所示。图8中Q1导通,Q2截止时,输出为低电平,为瞬间使输出为高,测试仪强加一瞬间电流脉冲,从Q1发射极反流过集电极,使输出端产生高电位,类似图9,Q2导通,Q1截止时,输出为高,为使输出为低,测试仪在输出处加一低电平,吸收由此产生从Q2流经的电流。因数字测试速度很快,电流脉冲时间远小于10ms(通常为5-10μs),这么短的脉冲不会造成芯片的损坏。

2.4 针床测试的局限

针床测试的局限主要体现在机械精度方面,我们不妨计算一下从PCB制作,夹具制造直至测试个环节带来的误差总和,就不难得出结论:

(1)夹具钻孔精度,状态很好的针床在钻厚度较厚的夹具板,精度很难控制在25μm以下,况且,对于某些高精度PCB测试用夹具,层数可高达8层之多。

(2)PCB测试时,PCB与夹具之间和夹具与设备之间对位精度,为了让夹具便于在针床上放置取下,若采用销钉定位,销钉与销钉孔的直径应相差10-20μm。

(3)PCB孔位与外层图形偏差。在多层PCB制造中,为避免内层破盘,提高合格率,常常采用层压后,根据各层图形相对位置,钻定位孔。层数越高,孔与外层图形对位置相差越大,PZB的上表面和下表面位置也可能相差±0.15mm。

(4)测试探针的移动。在多层夹具中,若有细小的偏差,造成探针摩擦或卡住,就会造成开路误报。密度过高造成夹具的各层强度下降,发生弯曲等现象,又会造成探针位置偏差。

(5)PCB尺寸稳定性和夹具与PCB尺寸一致性误差,对一类PCB,由于制造条件的差异(分批制造)环境温度、湿度会造成底片、基材的尺寸变化,导致同类PCB图形尺寸细小的差别。若板面较大,密度较高时,会直接影响测试精度,同样,夹具的尺寸也可能根据环境的变化出现微观差异,这些对测试准确性带来很大影响。

(6)PCB翘曲造成与测试针对位置变化,严重时,探针无法接触被测表面,产生误报。

综上所述,测试精度的局限是针床测试面临的最大问题,据统计,在保证重复测试正确性的 前提下,排除PCB上下两面位置的偏差,对100mm×100mm的PCB可测试的最小节距为0.25mm,对200mm×200mm的PCB可测试的最小节距为0.31mm,对300mm×300mm的PCB可测试的最小节距为0.44mm;对400mm×400mm的PCB可测试的最小节距为0.49mm。

需要指出的是,随着密度的变化,测试产品和测试成本都相应变化,产量与中心距的平方函数成正比,测试成本与中心距函数成反比。

另外,测试点数也是另一个局限因素,尤其是BGA广泛应用的今天,要求测试点密集,若PCB上分布的BGA较多,其间距有限,可能造成测试针分配不足的问题,对专用测试来讲,总的测试电枢也非常有限,对高密度封装板、局部测试点密集,可以被测试的面积也受到限制,例如,对常规的可测试面积为500mm×500mm,对高密度PCB可测面积仅为200mm×200mm,这就是总测试

在线测试 相关文章:

- 基于PC104的某型导弹地面电源相序检测与校正(06-27)

- 在线测试技术的现状和发展(一)(07-13)

- PCB LAYOUT工程师必须了解ICT飞针在线测试(02-27)

- 信号处理机的高速ADC模块动态性能在线测试(11-26)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)