DDS器件产生高质量波形:简单、高效而灵活

在一定程度上减轻抖动,因为对信号进行分频将在更长时期产生相同量的抖动,因而可以降低信号上的抖动的百分比。

噪声--包括相位噪声

采样系统的噪声取决于诸多因素,首要因素是参考时钟抖动,这种抖动表现为基波信号上的相位噪声。在DDS系统中,截断相位寄存器输出可能带来因代码而异的系统误差。二进制字不会导致截断误差。但对于非二进制字,相位噪声截断误差会在频谱中产生杂散。杂散的频率/幅度取决于代码字。DAC的量化和线性误差也会给系统带来谐波噪声。时域误差(如欠冲/过冲和代码错误)都会加重输出信号的失真。

应用

DDS应用可以分为两大类:

要求捷变频率源以进行数据编码和调制应用的通信和雷达系统

要求通用频率合成功能以及可编程调谐、扫描和激励能力的测量、工业和光学应用

两种情况下,都出现了一种走向更高频谱纯度(更低的相位噪声和更高的无杂散动态范围)的趋势,同时还存在低功耗和小尺寸的要求,以适应远程或电池供电设备的需求。

调制/数据编码和同步中的DDS

DDS产品首先出现于雷达和军事应用之中,其部分特性的发展(性能的提升、成本和尺寸等)已使DDS技术在调制和数据编码应用中日渐盛行。本节将讨论两种数据编码方案及其在DDS系统中的实现方式

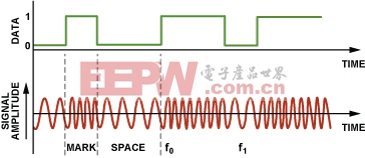

二进制频移键控 (BFSK,或简称FSK) 最简单的数据编码形式之一。数据的发射方式是使一个连续载波的频率在两个离散频率(一为二进制1,即传号,一为二进制0,即空号)之间变换。图4所示为数据和发射信号之间的关系。

图4.二进制FSK调制。

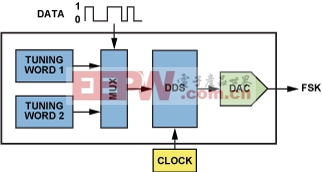

二进制1和0表示为两个不同的频率,分别为f0和f1.这种编码方案可以轻松在DDS器件中实现。代表输出频率的DDS频率调谐字被改变,以从将发射的1和0产生f0和f1.在ADI纯DDS产品系列中,至少有两款器件AD9834 和 AD9838另见附录),用户可以简单地将两个当前FSK频率调谐字编程进IC的嵌入式频率寄存器之中。要变换输出频率,则须用专用的引脚FSELECT选择含有相应调谐字的寄存器(见图5)

图5.利用AD9834或AD9838 DDS的调谐字选择器实现FSK编码。

相移键控(PSK) 是另一种简单的数据编码形式。在PSK中,载波的频率保持不变,通过改变发射信号的相位来传递信息。可以利用多种方案来实现PSK.最简单的方法通常称为二进制PSK(即BPSK),只采用两个信号相位:0°(逻辑1)和180°(逻辑0)。各位的状态取决于前一位的状态。如果波的相位不变,则信号状态将保持不变(低或高)。如果波的相位改变180°,即相位反转,则信号状态将改变(低变为高,或高变为低)。PSK编码可以轻松在DDS产品中实现,因为多数器件都有一个独立的输入寄存器(相位寄存器),可以加载相位值。该值被直接添加到载波的相位,而不改变其频率。更改该寄存器的内容将调制载波的相位,结果产生一个PSK输出。对于要求高速调制的应用,内置相位寄存器对的AD9834和AD9838允许其PSELECT引脚上的信号在预加载的相位寄存器之间变换,以根据需要调制载波。

更复杂的PSK采用四个或八个波相位。这样,每当相位发生变化时,二进制数据的传输速率将高于BPSK调制。在四相位调制 (正交 PSK),中,可能的相位角度为0°, +90°, ?90°, 和 +180°;每次相位变换可能代表两个信号因子AD9830, AD9831, AD9832, 和 AD9835 提供四个相位寄存器,通过连续更新寄存器的不同相位偏移,可以实现复杂的相位调制方案。

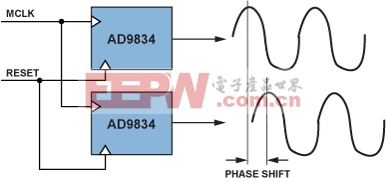

以同步模式利用多个DDS元件实现I/Q功能

许多应用要求产生两个或两个以上具有已知相位关系的正弦波或方波信号。一个常见的例子是同相和正交调制(I/Q),在这种技术中,在0°和90°相位角度从载波频率获得信号信息。可以用相同的源时钟来运行两个单独的DDS元件,以输出可以直接控制和操作其相位关系的信号。在图6中,用一个基准时钟对AD9838器件编程;相同的RESET引脚用于更新两个器件。这样,可以实现简单的I/Q调制

RESET必须在上电后以及向DDS传输任何数据之前初始化。结果可将DDS输出置于已知相位,使其成为共同的参考角度,以便同步多个DDS器件。当新数据被同时送至多个DDS器件时,DDS之间可以保持相关相位关系,或者通过相位偏移寄存器可以预测性调整多个DDS之间的相对相位偏移。AD983x系列DDS产品拥有12位相位分辨率,有效分辨率为0.1°。

图6.同步两个DDS元件。

有关同步多个DDS器件的更多信息,请参阅应用笔记AN-605 同步多个基于DDS的频率合成器AD9852.

网络分析

电子世界中的诸多应用都需要收集和解码来自网络的数据,例如模拟测量和光学通信系统。正常情况下,系统分析要求是为了以幅度和相位已知的频率模拟电路或系统,并分

DDS 相关文章:

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)