DDS器件产生高质量波形:简单、高效而灵活

和相移键控应用的适用性。

其他方案,包括集成DDS引擎的现场可编程门阵列 (FPGAs) --配合现成DAC以合成输出正弦波--虽然可以解决PLL的跳频问题,但也存在自身的缺陷。主要系统缺陷包括较高的工作和接口功耗要求、成本较高、尺寸较大,而且系统开发人员还须考虑额外的软件、硬件和存储器问题。例如,利用现代FPGA中的DDS引擎选项,要产生动态范围为60 dB的10 MHz输出信号,需要多达72 kB的存储器空间。另外,设计师需要接受并熟悉细微权衡和DDS内核的架构从实用角度来看(见表2),得益于CMOS工艺和现代数字设计技术的快速发展以及DAC拓扑结构的改进,DDS技术已经能在广泛的应用中实现前所未有的低功耗、频谱性能和成本水平。虽然纯DDS产品不可能在性能和设计灵活性上达到高端DAC技术与FPGA相结合的水平,但DDS在尺寸、功耗、成本和简单性方面的优势使其成为许多应用的首要选择。

表2.基准分析小结--频率产生技术(50 MHz)

同时需要指出,由于DDS器件从根本上来说是用数字方法产生输出波形,因此它可以简化一些解决方案的架构,或者为对波形进行数字化编程创造条件。尽管通常利用正弦波来解释DDS的功能和工作原理,但利用现代DDS IC也可以轻松产生三角波或方波(时钟)输出,由此消除了前一种情况的查找表以及后一种情况的DAC的必要性,因为集成一个简单而精确的比较器就够了。

DDS的性能与限制

图像和包络:Sin(x)xx滚降

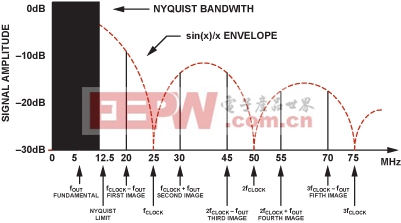

DAC的实际输出不是连续的正弦波,而是带有正弦时间包络的一系列脉冲。对应的频谱是一系列图像和混叠信号。图像沿sin(x)/x 包络分布(见图3中的|幅度|曲线图)。有必要进行滤波,以抑制目标频带之外的频率,但是不能抑制通带中出现的高阶混叠(例如,因DAC非线性所致)

奈奎斯特准则 要求,每个周期至少需要两个采样点才能重建所需输出波形。镜像响应产生于采样输出频率中 fCLOCK × fOUT . 在本例中,其中 fCLOCK = 25 25 MHz且fOUT = 5 MHz,第一和第二镜频出现在(见图3)fCLOCK × fOUT , o即20 MHz和30 MHz.第三和第四镜频出现在45 MHz和55 MHz.注意,sin(x)/x零值出现在采样频率的倍数处。当fOUT 大于奈奎斯特带宽 (1/2fCLOCK), 时,第一镜频将出现于奈奎斯特带宽之内,发生混叠(例如,15 MHz的信号将向下混叠至10 MHz)。无法用传统的奈奎斯特抗混叠滤波器从输出中滤掉混叠镜频

图3.DDS中的Sin(x)/x滚降。

在典型的DDS应用中,利用一个低通滤波器来抑制输出频谱中镜频响应的影响。为了使低通滤波器的截止频率要求保持于合理水平,并使滤波器设计保持简单,一种可行的做法是利用一个经济的低通输出滤波器将fOUT 带宽限制在fCLOCK频率的40%左右。

任何给定镜频相对于基波的幅度可用sin(x)/x公式来计算。由于该函数随频率滚降,因此基本输出的幅度将与输出频率成反比而降低;在DDS系统中,降低量为DC-奈奎斯特带宽范围的–3.92 dB.

第一镜频的幅度较大--基波的3 dB范围内。为了简化DDS应用的滤波要求,必须制定频率计划,并分析镜频和sin(x)/x幅度响应在fOUT 和fCLOCK目标频率下的频谱要求。在线互动设计工具 支持ADI DDS产品系列,可以快速、轻松地仿真镜像频率大小,并允许用户选择镜像位于目标频带之外的频率。更多有用信息,请参阅更多信息和有用的链接部分。

输出频谱中的其他不需要的频率(如DAC的积分和微分线性误差、与DAC相关的突波能量和时钟馈通噪声)不会遵循sin(x)/x滚降响应。这些不需要的频率将以谐波和杂散能量出现在输出频谱中的许多地方--但其幅度一般会远远低于镜频响应。DDS器件的一般本底噪声由基板噪声、热噪声效应、接地耦合和其他信号源耦合等因素累积组合决定。DDS器件的本底噪声、性能杂散和抖动受到电路板布局、电源质量以及--最重要的是--输入参考时钟质量的深刻影响。

抖动

完美时钟源的边沿将以精确的时间间隔发生,而该间隔永远都不会变化。当然,这是不可能的;即使最好的振荡器也是由不理想的元件构成,具有噪声等缺陷。优质的低相位噪声晶体振荡器的抖动为皮秒级,而且是从数百万个时钟边沿累积起来的。导致抖动的因素有热噪声、振荡器电路不稳定以及电源、接地和输出连接等带来的外部干扰等,所有这些因素都会干扰振荡器的时序特性。另外,振荡器受外部磁场或电场以及附近发射器的射频干扰的影响。振荡器电路中,一个简单的放大器、反相器或缓冲器也都会给信号带来额外的抖动。

因此,选择一个抖动低、边沿陡的稳定的参考时钟振荡器是至关重要的。较高频率的基准时钟允许较大的过采样,而且,通过分频可以

DDS 相关文章:

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)