基于DSP的数字闭环功放控制系统

本文提出一种基于DSP的数字闭环功放控制系统,通过检测正反向功率电压确定输出功率上升或下降的最佳步径,按该步径增加或者减少功放输出功率,并随时检测输出功率是否超过额定输出功率,如超过额定输出功率,根据求出的最大下降步径进行相应的调整,及时将功放输出功率减小到额定功率,这样形成一个闭环控制系统。由于采用DSP为处理核心,处理速度和计算精度都得到保证。这样既能保证功放的安全可靠又可以使功放尽量输出可发射的最大功率。

系统硬件结构

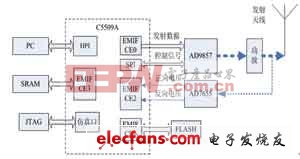

整个系统由C5509A、AD9857、AD7655组成,系统框图如图1所示。

图1 系统结构框图

从图1可以看出,DSP是核心控制单元;AD9857用于发射数据,进行上变频,并输出模拟数据到功放,再经过天线发射出去,AD9857的控制信号由DSP的SPI接口实现。AD7655负责采集功放的正向和反向电压值,将电压值回送到DSP,DSP根据电压值进行功放控制。SRAM存储发射的基带数据,以及实时计算发射基带数据的中间变量。Flash保存DSP所需要的程序,供DSP上电调用;DSP和PC之间使用HPI口,使用PCI桥芯片,实现和PC的连接。DSP对AD9857、AD7655、SRAM以及Flash都是经过DSP的EMIF接口连接,EMIF接口是DSP的外部存储器接口(External Memory Interface),可以方便的和外部Flash、异步SRAM等设备连接。本系统的外部设备数据通信速率均较低,最高数据传输速率为AD9857的48Mb/s,C5509A的EMIF接口适合满足其速度要求。

闭环控制算法

对发射机功放输出功率的典型控制方法是根据驻波比来调整发射机的输出功率。发射机的正、反向功率检测电压与功放输出功率及驻波比之间的数值关系如下。

正向功率检测电压:

(1)

反向功率检测电压:

(2)

驻波比:

(3)

式中,VF_Full表示当功放输出最大额定功率时对应的正向功率检测电压,PFWD表示功放输出的正向功率,PREV表示反向功率,PF_Full表示功放输出的最大额定功率。

根据正、反向功率检测电压计算出允许功放输出功率的最大上升或下降步径来控制功放输出功率。

设PR_Full为功放能承受的最大反向功率,并且PR_Full=b(常数);POUT为反向电压达到VR_Limit时的输出功率;输出额定功率时对应的正向功率检测电压VF_Full=a(常数);PF_Full/PR_Full=n(常数)。这三个常数都由功放的指标确定。

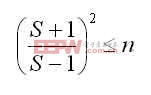

根据式(3),在反向电压达到VR_Limit时的驻波比如下:

(4)

(5)

由于POUT最大为b,所以有:

(6)

当

,也就是说,此时输出额定功率。

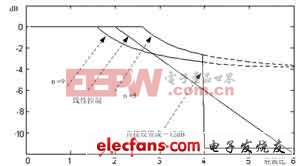

根据上面的讨论,功放输出额定功率受限于功放的PF_Full/PR_Full的比值n。在一定驻波比情况下,功放是无法输出额定功率的,例如,驻波比为3,n为3无法输出额定功率。此时,功放能够输出的功率将小于额定功率,但可以输出的最大功率是多少呢?根据式(5),图2画出了功率控制曲线图。图中设定输出额定功率为0dB,为了比较,图中给出了n=9和n=5以及线性控制方法的曲线。

图2 功率控制曲线

线性控制方法为根据驻波比直接进行线性比例控制方法。线性控制不考虑功放自身的情况,所以其控制简单,比较容易实现。但控制粗糙,对于质量好的功放,没有充分发挥其性能,对于质量差的功放,又容易烧毁功放。

如图2中n=9时,此时功放的指标较差,一般情况下不能使用。尤其在使用线性控制方法时,工作时间稍长就会烧毁功放。这是因为,线性控制方法在驻波比等于2时,输出额定功率。而使用基于闭环控制算法后,由于n=9,在驻波比等于2时不能输出额定功率,确保不会烧毁功放。

如图2中n=5时,此时功放的指标较好,使用线性控制方法,仍然严格遵守图中斜线,闭环控制方法的功率输出则明显偏大,充分利用了功放的特性。

实际工作情况下,驻波比大于4时功放和天线都将明显变差,此时为了保证系统的稳定,将直接将曲线设置成 -12dB,使得功放的输出维持在较低的水平。

实验

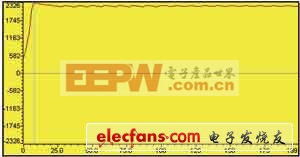

为了验证本文提出的方法的有效性和实用性,将该方法应用于短波和超短波电台,图3为其功率控制收敛曲线。从图中可以看出,功率控制大概在10次步径后达到稳定状态,稳定后曲线波动较小,功率输出几乎恒定。

图3 功率控制收敛曲线

总结

本文介绍了对发射机功放输出功率进行控制的闭环控制算法,以及系统组成。通过计算正反向功率检测电压,确定允许功放输出功率升降的最大步径来控制功放输出功率。整个系统采用DSP和AD9857来实现,经过短波和超短波系统测试,基于闭环算法的功放输出效率明显高于其他典型的线性控制算法,在确保功放安全的情况下,对提高功放的效率具有实用价值。

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)