基于DM6446中的高清数字视频显示接口设计方案(二)

缓冲区用于保存窗口中的像素数据,缓冲区的起始位置由xxx_ADR 指定,窗口数据行偏移量由xxx_OFST 指定。起始位置寄存器xxx_ADR 的值是可以动态改变的,并且改变后的值只有在下一帧同步信号(VSYNC)到来时才起作用,这样我们便可以在内存中开辟多个窗口缓冲区,以增加窗口的显示效率。这里配置OSD 窗口主要是为VENC提供显示数据,其他有关OSD模块的配置可以参考其说明文档[3],这里不赘述。

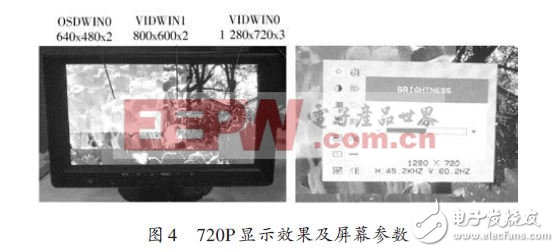

3.3 实际显示效果

在实际显示OSD 窗口的过程中,要保证VIDWIN0的分辨率不超过VENC中显示的有效分辨率(HVALID xVVALID),而其他所有OSD 窗口的范围都不能超出VIDWIN0,否则将会导致画面显示不正常。虽然VENC输出分辨率已经能够达到1 080P和WUXGA,但在这个高清分辨率显示下,只有VIDWIN0能够用于视频显示,其他窗口必须保持关闭状态,这主要受制于OSD 模块的传输带宽。而在VENC 配置为720P 分辨率的情况下,能够稳定实现多个窗口同时显示,如图4所示。

在这里,VIDWIN0、VIDWIN1、OSDWIN0 的大小分别为1 280×720,800×600 和640×480,像素格式分别为3 字节RGB888、2 字节的YUV422 和2 字节的RGB565.此时显示器显示的行同步信号频率为45.2 kHz,帧同步频率为60.2 Hz,分辨率为1 280×720,说明高清数字视频显示接口工作正常,能够稳定实现在高分辨率下的多窗口同时在屏显示。

4 结语

本文利用DM6446的数字视频输出接口,搭配DVI驱动芯片TFP410, 通过对芯片内部时钟以及视频编码模块(VENC)时序发生器的正确配置,实现了电路结构简单、配置灵活的高清数字视频显示接口。在目标板上,本文提出的高清数字视频显示接口方案能够稳定显示720P、1 080P 及WUXGA 分辨率的画面,说明该方案易用、可行,具有实用性,对于扩展基于DM6446的数字视频显示接口具有重要参考意义。

- 基于DM6446中的高清数字视频显示接口设计方案(一)(10-31)

- 高清晰电视基础:揭密显示屏幕背后的电视技术(01-13)

- 并不总是坏消息,FPD产业精彩才刚刚开始(01-11)

- 全高清电视的电源发展趋势解析(04-16)

- 高清视频CMOS电流舵数/模转换器的设计(06-07)

- 在高清显示器上优化标清视频(08-15)