一种14位210MSPS校准电流DAC设计

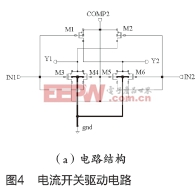

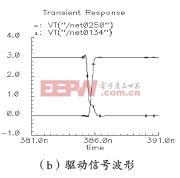

电流开关驱动电路及其仿真结果波形如图4所示。

?

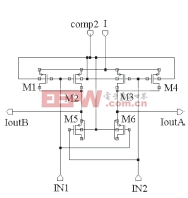

在本设计中,电流开关是PMOS管差分对的结构,并设计在同一N阱中,从而较好地避免了开关噪声和浪涌能量等不利影响。同时为了降低时钟馈通的影响,我们加入了冗余晶体管结构。电流开关电路结构如图5所示。

图5中的电流开关由6个PMOS管组成,M1和M2并联,M3和M4并联,他们构成了一对差分开关,而M5和M6是冗余晶体管。信号IN1与IN2是上级电路——电流开关驱动电路输出的互补开关控制信号,由于他们的高电平是comp2,所以本电路中晶体管的衬底都接comp2,这样就能够降低偏衬效应引起的噪声。

3.3?电流调整电路

本设计可以通过熔丝编程技术,对高中低位的电流进行调整,从而降低芯片的INL、DNL和增益误差,使芯片的性能得以提高。对电流的调整需要控制成比例电流的添加或抽取,但是此控制要通过电流源开关实现,控制这些开关的就是熔断丝电路阵列。在编程熔断状态下,通过编程来熔断相应的熔断丝,以使该熔断丝电路控制的电流源开关处于常开状态,从而实现对芯片线性度的永久修正。编程端口对熔断丝阵列的控制是通过行列译码器实现的。

4?测试结果

通过电路和版图优化设计,以及采用校准技术,转换器性能有了较大提高。表1给出了采用0.35μm?1P3M?CMOS工艺得到的样片电路测试结果。在输出5.04MHz(@SPAN?4MHz)时,其SFDR为84.9dB。

参考文献:

[1]Yang?C,et?al.A?serical-link?transceiver?based?on?8-G?samples/s?A/D?and?D/A?converters?in?0.25-μm?CMOS.IEEE?J.Solid-State?Circuits,2001,36(NOV):?293-301

[2]Bastos?J,et?al.A?High?Yield?12-bit?250-MS/s?CMOS?D/A?converter.IEEE?custom?integrated?circuit?conference.1997:431-434

[3]孔瀛,王宗民,许军.一种16位高速数模转换器(DAC)的设计与实现.?电子产品世界,2014(1):71-73

[4]张倬,王宗民,周亮,等.低功耗8-bit?200MSPS时间交织流水线ADC.电子产品世界,2013(12):71-73

[5]蔡伟,杨松,谭博.8位1.0GSPS?ADC芯片MXT2001原理与应用.电子产品世界,2013(11):62-63

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- 如何使低功耗放大器在便携式产品中提高性能(10-03)

- 一种折叠共源共栅运算放大器的设计(11-20)

- 高速DAC AD9712B/AD9713B的原理和应用(11-30)

- 混频器用作开关,可使 DAC 采样频率加倍(01-22)

- 什么是DAC(数模转换器)(01-24)