TLK6002/10002 Local Deep Loopback 的原理及注意事项

摘要

TI 提供的TLK6002, TLK10002 等多种速率的通用Serdes 芯片,在不同的领域得到了广泛的应用。特别在光纤拉远的应用中,由于TLK6002, TLK10002 独特的配置灵活性和优良的适配宽容度,已成为业界的主流配置。

TLK6002, TLK10002 所提供了包括“近端深度环回”,“近端浅度环回”,“远端深度环回”和“远端浅度环回”在内的多种环回模式,方便设计者在调试过程甚至在实际使用中迅速定位故障来源,降低了开发的难度,并提高了目标设备的易维护性。

不同的环回模式仅仅需要通过对于单个的配置寄存器配置即可实现。但在实际的使用案例中,我们往往发现当TLK6002, TLK10002 与光模块相连时,在使用“近端深度环回”模式时,存在一定的失败几率,误码率较高,而这时候切换至“正常通路”模式后,往往系统工作正常,并不存在误码率过高的问题。

本篇应用手册将对这一现象进行讨论,并提出解决方案。

1 TLK6002/TLK10002 环回模式介绍

TLK6002/TLK10002 作为业界领先的独立通用Serdes 芯片,由于速率灵活可配,被广泛的应用在不同的领域。特别在光纤拉远的应用,成为了独立通用Serdes 的不二选择。

由于在光纤拉远的应用中,出现误码时需要分段逐级排查,来定位系统中产生误码的位置,再进一步的调试维护解决问题。

TLK6002/TLK10002 提供了丰富的环回模式。

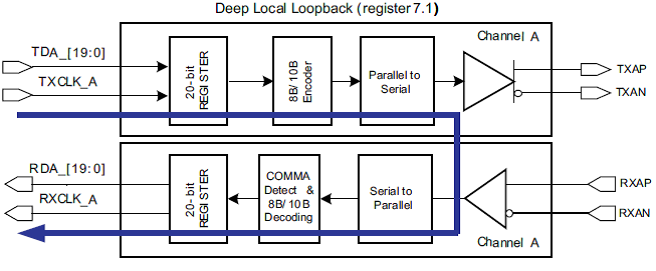

a. 近端深度环回,从并行到并行方向,链路经过了Serdes 内部,除高数CML 缓冲器之外的所有电路部分;

图一 近端深度环回

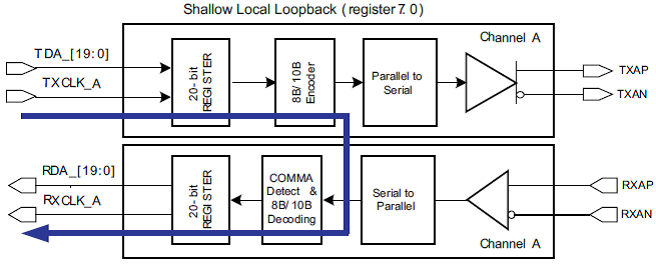

b.近端浅度环回,从并行到并行方向,链路仅经过8b/10b 的编解码机,隔离了芯片内部的串行解串的电路部分;

图二 近端浅度环回

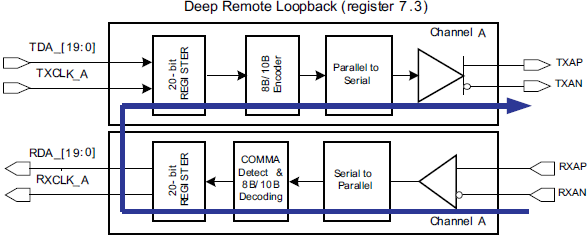

c.远端深度环回,从串行到串行方向,链路经过了Serdes 内部所有电路部分;

图三 远端深度环回

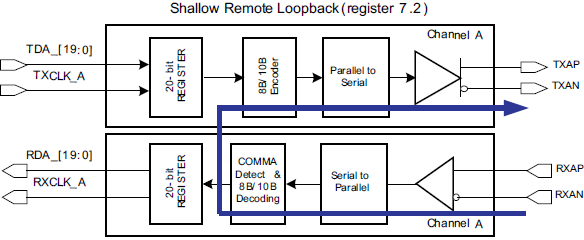

d. 远端浅度环回,从串行到串行方向,链路经过了Serdes 内部,除并行FIFO 之外的所有电路部分;

图四 远端浅度环回

2 TLK6002/TLK10002 近端深度环回在与光模块相连时的应用实例

在光纤拉远的应用中,由于距离较近,因此多使用近距离的SFP+ 6Gbps ~ 10Gbps 规格的光模块。

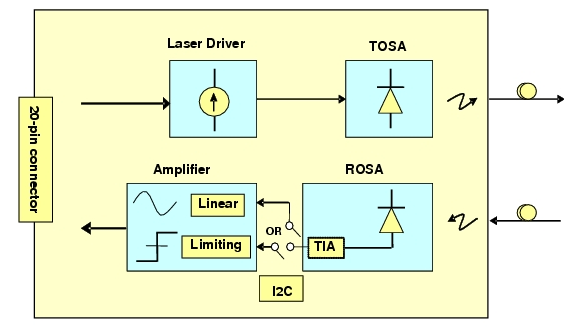

a. SFP+光模块的结构与特性

由于SFP+是一种无CDR 的光模块,因此在接收方向的整条链路中,仅仅实现光电管IV 变换后对电压波形进行线性或限幅放大,将串行的光信号转化成为串行电信号。因为在数据的恢复应用中,对于输入眼图有严格的限定,因此为了保证达到标准的限定,链路中IV 变化率和电压的增益均较高。TLK6002/TLK10002 输入端的CML

图五 SFP+光模块系统结构

以在市场上主流的SFP+方案为例,ONET8531T,TIA,作为IV 变换级,提供了高达4.5K 的跨阻;而ONET8501PB 作为放大器,对于小信号提供了高达34dB 的增益。

当有光信号输入到光模块时,因为TIA 和限幅放大器中的AGC 自动增益控制电路的作用,线路增益将会以实现摆幅为目的的压缩,因此我们能够得到一个低噪声的串行电信号。

而当光信号被关闭,由于ROSA 中的PIN 管暗电流的存在,会向TIA 输出噪声电流。因为暗电流较低,所以无论TIA 的跨阻以及限幅放大器的增益均会被AGC 调高至最大值,而经过IV 变化和限幅放大器的转换放大以后,在光模块的输出端我们便能够观察到幅度较高的热噪声。

由于光模块内的噪声,以及PCB 板上存在的各种串扰噪声等,导致在SerDes 接收端管脚有一定幅度的随机噪声输入。

b. TLK6002/TLK10002 近端深度环回模式下内部的状态

因为从一般意义上来看,系统排查工作存在着单步变化的要求,因此近端深度环回被设计成为如下图所示的物理层的单个开关的连通,这样在保证所有状态机不变的情况下,允许系统将输出的串行信号输入到接受通路。

图六 TLK6002/TLK10002 近端深度环回内部连接

而在这个状态下,因为其他电路均保持使能,因此TX 方向,CML 驱动器保持使能状态,能够向外部输出信号; RX 方向的CML 驱动器也保持使能状态,输入信号经过驱动器后,与环回信号叠加,输送给Serial to Parallel 部分。

c. CML 驱动器对于输入噪声的响应

CML 电平在高速信号中被广泛的采用,由于各个国际标准化组织并没有针对它出台严格的标准,因此在实际的应用中,芯片级的实现存在着稍许不同。但由于电路应用已经成熟,因此形成了相对统一的电路架构。

如下图所示,CML 的缓冲器,以差分放大器的形式构成。对于高于闸值的高低电平能够使得差分对管导通或截止,来得到高低电平的变换,而对于小于闸值的信号来说,将以由MOS 管跨导,Rdn 以及负载电阻,和

- DPA-Switch为应对PoE受电设备设计挑战提供有效解决方案(11-06)

- 在射击探测器中增加口径确定功能的简单电路(11-13)

- 用LatticeXP FPGA 桥接吉比特媒体独立接口(01-18)

- 单片机与串行AD转换器TLC0834的接口设计(01-22)

- 8位高速A/D转换器TLC5510的应用(02-16)

- 改善平板显示器的音频性能(02-13)