用于电池测试和化成的双向同步PWM控制器

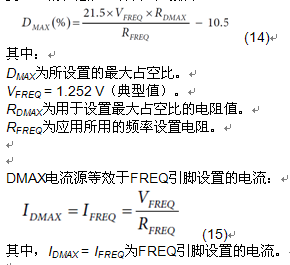

间连接一个电阻,便可将最大占空比设置为0%到97%的任意值,计算公式如下:

图31. RDMAX与占空比的关系,RFREQ = 100 kΩ,VCOMP = 5 V

ADP1974的最大占空比为97%(典型值)。 如果DMAX电阻设置的最大占空比大于97%,ADP1974将默认使用内部最大值。 如果97%的内部最大占空比对应用足够,应将DMAX引脚接VREG或使其保持浮空。

DMAX引脚和接地层之间连接的CDMAX电容必须为47 pF或更大。

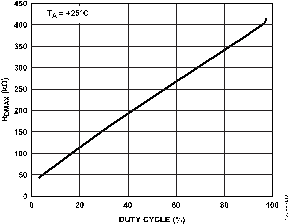

调整软启动周期

ADP1974具有可编程软启动功能,可防止启动期间输出电压过冲。 软启动图参见图22。 利用下式计算使能开关前的延迟时间(tREG):

举个例子,一个采用20 V输入和10 nF电容的设计将有1 ms的延迟和2.5 V/ms的斜坡率。

CSS电容不是ADP1974必需的。 不使用CSS电容时,内部5 μA(典型值)电流源立即将SS引脚电压拉到VREG。 不使用CSS电容时,ADP1974内部便没有软启动控制,系统可能会在启动期间产生较大的输出过冲和峰值电感尖峰。 不使用CSS电容时,应确保启动期间的输出过冲不能大到触发打嗝限流。

PCB布局指南

为了实现较高的效率、良好的调节性能和出色的稳定性,PCB布局布线必须合理设计。

设计PCB时,应遵守下列原则(框图见图20,引脚配置见图2)。

· VIN的低有效串联电阻(ESR)输入电源电容(CIN)应尽可能靠近VIN和GND引脚,以使电路板寄生电感注入器件的噪声最小。

· VREG的低ESR输入电源电容(CVREG)应尽可能靠近VREG和GND引脚,以使电路板寄生电感注入器件的噪声最小。

· 用于SCFG、FREQ、DMAX和SS引脚的元件应靠近相应的引脚放置。 将这些元件统一连接到模拟接地层,以便与GND引脚形成开尔文连接。

· 从COMP引脚到关联器件(如AD8450)的走线应尽可能短。 此走线不应放在开关信号附近,可能的话应将其屏蔽起来。

· 任何用于SYNC引脚的走线或元件应远离敏感的模拟节点。 使用外部上拉电阻时,最好在上拉电阻的电源和GND之间使用一个本地0.1 μF旁路电容。

· 从DH和DL引脚到外部元件的走线应尽可能短,以使寄生电感和电容最小,避免影响控制信号。 DH和DL引脚是开关节点,其相关布线不应靠近任何敏感的模拟电路。

· 使高电流走线尽量短、尽量宽。

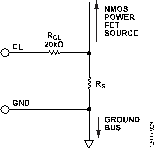

· 将ADP1974的接地连接直接连到电流检测电阻(RS)的接地连接。

· 通过一个20 kΩ电阻将CL直接连到RS。

· 从图32所示的接地连接进行如下连接:

· GND引脚连接到RS的接地点

· 系统电源接地总线连接到RS的接地点

· 构建一个具有一个主机和多个从机的系统时,应考虑如下事项以使与SYNC引脚相连的走线电容最小:

· 对于仅有几个从机的小型系统,在主机SYNC信号和从机SYNC输入引脚之间串联一个电阻可限制走线电容,降低可能会把噪声注入主机的快速地电流。

· 对于较大型应用,串联电阻不足以隔离主机SYNC时钟。 在较大系统中,使用外部缓冲器来降低走线电容。 外部缓冲器具有驱动能力,可支持较大数量的从机。

图32. 推荐RS开尔文接地连接

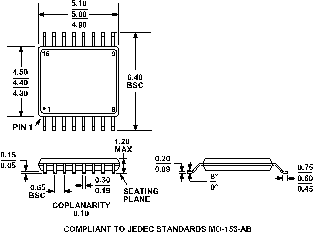

外形尺寸

图33. 16引脚超薄紧缩小型封装[TSSOP]

(RU-16)

图示尺寸单位:mm

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 改善 PWM 电源控制器低负载运行的缓冲放大器和 LED(01-16)

- 负输出罗氏变换器实用性剖析(01-09)

- 一种新型ZCS-PWM Buck变换器研究(02-20)

- PWM技术实现方法综述(02-19)

- 基于HPWM技术的大功率正弦超声波逆变电源(02-26)