用于电池测试和化成的双向同步PWM控制器

(ICL) × (RCL) ? (IPK) × (RS) (3)

VNC (BUCK) = (ICL) × (RCL) + (IVL (NEG)) × (RS) (4)

升压(循环)模式:

VCL (BOOST) = (ICL) × (RCL) + (IPK) × (RS) (5)

其中:

VCL (BUCK) = 300 mV(典型值)。

ICL = 20 μA(典型值)。

RCL = 20 kΩ。

IPK为峰值电感电流。

VNC (BUCK) = 450 mV(典型值)。

IVL (NEG)为谷值电感电流。

VCL (BOOST) = 500 mV(典型值)。

在降压和升压两种工作模式下,ADP1974的峰值电流限值相同。RCL和RS电阻的容差建议为1%或更好。

调整工作频率

如果SCFG引脚接VREG,迫使VSCFG ≥ 4.53 V,或者如果SCFG引脚保持浮空且内部连接到VREG,则ADP1974以RFREQ设置的频率工作,SYNC引脚以编程设置的频率输出一个时钟。当VSCFG ≥ 4.53 V时,SYNC引脚的输出时钟可用作需要同步的应用中的主时钟。

如果VSCFG ≤ 0.5 V,则SYNC引脚配置为输入,ADP1974用作从机。作为从机,ADP1974与施加于SYNC引脚的外部时钟同步。如果施加于SCFG引脚的电压为0.65 V < VSCFG < 4.25 V,并且在SCFG和地之间连接一个电阻,则SYNC引脚配置为输入,ADP1974与施加于SYNC引脚的外部时钟的相移版本同步。

无论ADP1974是以主机还是从机工作,都要利用上面的公式精心选择RFREQ。

选择主机的RFREQ

当VSCFG ≥ 4.53 V时,ADP1974用作主机。作为主机,ADP1974以外部RFREQ电阻(连接在FREQ和地之间)设置的频率工作,并且ADP1974在SYNC引脚上输出一个编程频率的时钟。

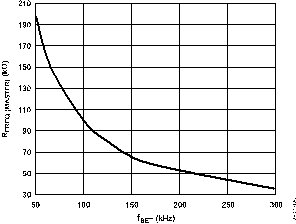

图28显示了RFREQ (MASTER)值与编程开关频率的关系。

图28. RFREQ (MASTER)与开关频率(fSET)的关系

要获得所需的主机时钟同步频率,请使用下式计算RFREQ (MASTER)值:

其中:

RFREQ (MASTER)为用于设置主机频率的电阻(单位为kΩ)。

fSET为开关频率(单位为kHz)。

选择从机的RFREQ

驱动VSCFG < 4.53 V时,ADP1974配置为从机。 作为从机,ADP1974以施加于SYNC引脚的外部时钟频率工作。为确保正确同步,利用下式选择RFREQ以将频率设置为略低于主时钟频率的值:

RFREQ (SLAVE) = 1.11 × RFREQ (MASTER) (6)

其中:

RFREQ (SLAVE)为适当缩放从机频率的电阻值,1.11为用于同步的RFREQ从机与主机之比。

RFREQ (MASTER)为与施加于SYNC引脚的主时钟频率相对应的电阻值。

从机频率设置为略低于主机频率,以便ADP1974的数字同步环路能够与主机时钟周期同步。从机可与高于从机时钟频率2%到20%的主机时钟频率同步。设置RFREQ (SLAVE)比RFREQ (MASTER)大1.11倍,可使同步环路大致在调整范围的中心运行。

外部时钟相移编程

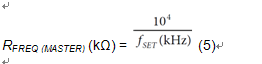

如果从机不需要相移,各从机的SCFG引脚须接地。对于需要施加于从机SYNC引脚的同步时钟的相移版本的器件,应在SCFG和地之间连接一个电阻(RSCFG)来设置所需的相移。 对于所需相移(φSHIFT),为了确定RSCFG,首先应计算从机时钟频率(fSLAVE)。

其中:

tDELAY为相位时间延迟(单位为μs)。

φSHIFT为所需相移。

最后,使用下式计算tDELAY:

RSCFG (kΩ) = 0.45 × RFREQ (SLAVE) (kΩ) + 50 × tDELAY (μs) (10)

其中:

RSCFG为所需相移(单位为kHz)的对应电阻。RSCFG与tDELAY的关系曲线参见图19。

使用相移特性时,应将一个47 pF或更大的电容与RSCFG并联。

或者,SCFG引脚也可利用一个电压源来控制。使用独立电压源时,确保所有情况下VSCFG ≤ VREG。通过EN引脚或UVLO禁用ADP1974时,VREG = 0 V,必须相应地调整电压源以确保VSCFG ≤ VREG。

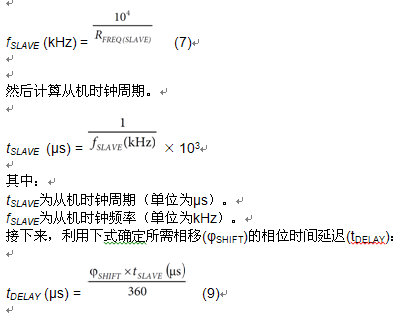

图29显示了ADP1974的内部电压斜坡。该电压斜坡是一个精确控制的4 V p-p斜坡。

死区时间编程

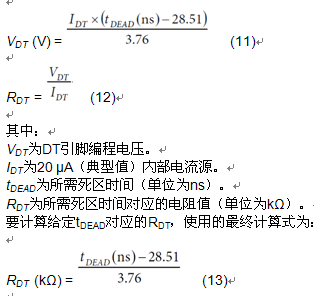

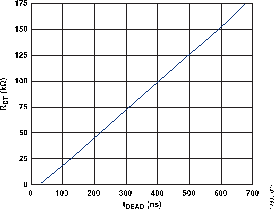

要调整DH和DL同步输出的死区时间,应在DT和GND之间连接一个电阻(RDT)并用一个47 pF电容予以旁路。利用图30选择给定死区时间对应的RDT,或利用下式计算RDT。要获得单个RDT计算式,可将VDT和RDT的计算式合并。

图30. DT引脚电阻(RDT)与死区时间(tDEAD)的关系

最大占空比编程

ADP1974的设计最大内部占空比为97%(典型值)。在DMAX和地之

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 改善 PWM 电源控制器低负载运行的缓冲放大器和 LED(01-16)

- 负输出罗氏变换器实用性剖析(01-09)

- 一种新型ZCS-PWM Buck变换器研究(02-20)

- PWM技术实现方法综述(02-19)

- 基于HPWM技术的大功率正弦超声波逆变电源(02-26)