基于Verilog HDL的SVPWM算法的设计与仿真

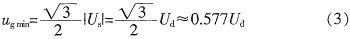

能使用常规乘除法,只能通过左移、右移分别进行乘以2、除以2的运算,且当t1+t2=tg时,ug的最小值为:

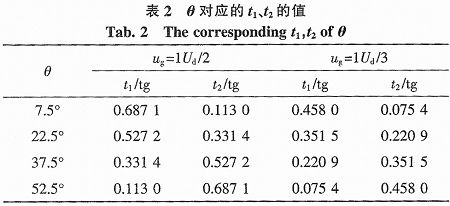

所以设计ug=1Ud/2和ug=1Ud/3两组基本时间参数,跟据式(2)分别得到t1、t2的值如表2所示。转矩输入信号的MSB选择基本时间参数,其他比特位数值表示基本时间参数右移位数(即基本时间参数除以该数值)。

图3中T0、T7均等于t0/2=(tg-t1-t2)/2,根据转矩输入信号选择基本时间参数,并进行向右移位操作,计算出不同θ对应的7个开关状态的持续时间。

3.3 状态机模块

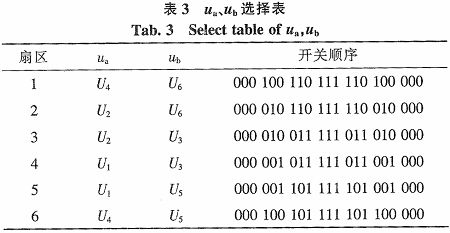

状态机模块利用控制时钟进行状态转换,矢量状态有24个,开关状态有7个,24个矢量状态从前到后循环转换,每个矢量状态下的7个开关状态依先后顺序转换一遍,开关顺序如表3所示,各自持续时间通过计数器计数值与对应时间参数比较而得到。如图3所示,设两个非零电压矢量中,与零矢量U0相邻的是ua另一个是ub,可知ua必须是U4、U2、U1中的一个,ub必须是U6、U3、U5中的一个,具体如表3所示。

3.4 波形产生模块

波形产生模块根据矢量状态和开关状态,决定三相的输出电压矢量(U0,U1,…,U7)。24个矢量状态分别位于6个扇区中,依据矢量对应的开关状态选择输出电压矢量,各扇区中矢量的开关顺序如表3所示。

4 仿真验证

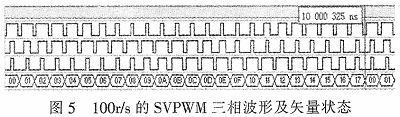

使用Active-HDL软件进行仿真验证,建立仿真模块,提供系统时钟和复位信号,设定不同转速输入信号及转矩输入信号进行仿真,下面以部分仿真截图对设计进行验证。

4.1 转速调节仿真

转速调节仿真时,设定相同转矩ug=1Ud/3,对比两种不同转速仿真如下。

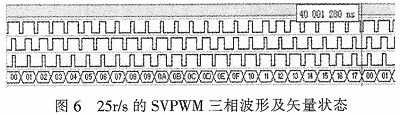

由表1可知,系统时钟分频数设定为1时,对应转速为100 r/s,即周期为10 ms,如图5所示,最下面是24个矢量状态的十六进制数,仿真显示一个周期约10 ms,由于计数器值为整数,计算时对小数进行了四舍五人,并且仿真开始存在一定时间对变量进行初始化,所以存在很小的误差,结果符合预期。系统时钟分频数设定为4时,对应转速为25 r/s,即周期为40ms,如图6所示,仿真结果符合预期。

4.2 转矩调节仿真

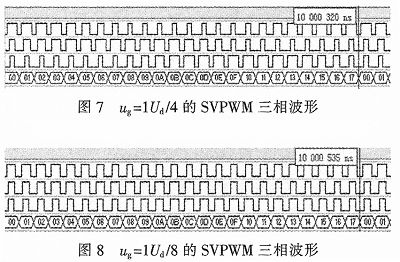

转矩调节仿真时,设定相同转速100 r/s,对比3种不同转矩仿真结果。

图5(见4.1小节)、图7、图8分别是ug=1Ud/3、ug=1Ud/4、ug=1Ud/8时的仿真结果。由三相电机PWM调制原理得知,三种转矩情况下,波形的基波分量的绝对值依次降低,仿真波形符合预期。

5 结束语

文中针对24矢量7段式SVPWM算法设计实现方法,基于Verilog HDL进行软件仿真,主要仿真不同转速、转矩时的SVPWM波形、验证了设计达到了预期的效果。

在SVPWM实际应用中,通常都会插入死区时间,防止逆变器桥臂发生瞬间短路,本文的设计实现没有对此进行设计,后期可以改进这一点,同时,可以利用相关FPGA/CPLD综合软件下载到硬件,进行硬件实现。

同步电动机 电压型逆变器 Verilog HDL 相关文章:

- 伺服控制系统中高精度电流采样的设计(04-13)

- 永磁同步电动机原理(04-08)

- PCM串行数据流同步时钟提取设计(02-25)

- 一种数模混合SoC设计协同仿真的验证方法(04-09)

- 基于FPGA的∑-△D/A转换器的设计与实现(04-23)

- 基于ISP芯片的可编程数字移相器设计(06-23)