基于多片高速D/A AD9739的多通道信号模拟器

CLK944供给4片AD9739时钟的线路需做到等长;FPGA与AD9379之间的时钟同步引脚DCO与DCI需分别等长;时钟Buffer CDCLVD1213供给AD9739的同步时钟线路需等长;FPGA与4片AD9739的数据输入线路需全部等长。

其次,在DA配置上,输出同步信号(SYNC_OUT)的AD9739要配置成主模式(Master Mode),其余的AD9739均配置成从模式(Slave Mode)。

最后,FPGA进行相位补偿,如图1所示,通常情况下FPGA数据产生使用的是主片AD9739输出的DCO时钟,若经过以上两步,4片AD9739的输出仍不同步,FPGA则可替换用其他从片AD9739输出的DCO时钟产生数据。若此时同步仍不理想,就需要在FPGA程序中进行人工补偿,即人为地在同步不佳的某一路中添加相位延迟,使其能达到同步效果。

4 测试数据

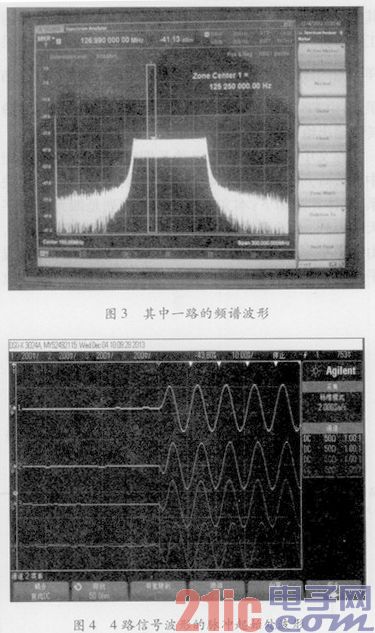

采用时钟芯片提供AD9739 1.6 GHz的工作时钟,AD9739工作于Normal Mode,利用上述硬件平台实现初始频率100 MHz,带宽100 MHz,脉宽10 μs,各路信号间有一定相位关系的4通道线性调频信号,其时域波形如图2所示,用频谱仪分析其中一路的频域波形如图3所示。本文最终产生的4路信号波形之间的相位差是一个变化过程,限于篇幅,无法将其变化过程详细展现,取其中间某组脉冲信号将4路信号的脉冲起始处展开,如图4所示。可以直观地看出,4路信号对齐的效果良好,相位差存在且较为明显。

5 结束语

将FPGA与多片高速D/A AD9739结合,经信号同步,通过DDS产生中心频率在0~800 MHz之间,调频带宽600 MHz以内且4路有一定相位关系的线性调频信号,此方案在某空中平台定位验证系统中作为测试辐射源。经验证,此系统能良好地模拟多元天线阵列所接收到的信号,同时定位系统可根据模拟器的输出信号定位出目标辐射源的位置参数。

本文多路信号之间只有相位信息不同,经扩展后,亦可产生多路之间频率、幅度、频率变化率等参数不同的多路宽带线性调频信号,即在FPGA中使用DDS产生多路信号时使用不同的初始参数。受限于D/A的工作频率,输出的信号频率较低。硬件布线未严格等长以及元器件的误差使4路同步信号的时间差在ns级以上,对于某些需要精确定位的系统并不适用。如何进一步提高多通道之间的同步性,依然是探索研究的重要课题。

多通道 高速D/A AD9739 宽带线性调频信号 相位差 相关文章:

- 利用Σ-Δ ADC在工业多通道数据采集系统中进行信号调理(10-23)

- 基于PCI总线模块的多通道串行数据采集系统设计(11-01)

- 多通道A/D转换控制模块的设计与实现(09-20)

- 模数转换器组成的可编程40通道输出电路的设计方案(03-03)

- 数字电位器在雷达多通道接收机中的应用(03-15)

- 大功率LED照明方案(11-01)