2.5 Gbps收发器中1:2解复用电路的设计

时间:10-16

来源:互联网

点击:

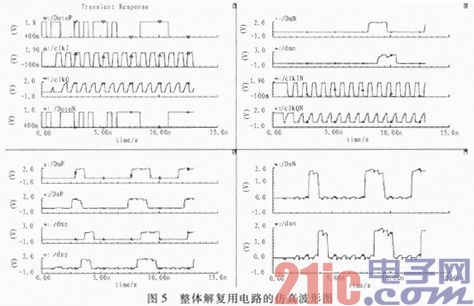

用数模混合的方法进行仿真。输入数据采用VerilogHDL语言编写的伪随机序列,采用Cadence的SpcctreVerilog进行仿真。仿真结果如图5所示,比较输入数据和由主时钟采样输出的数据,可以看出电路的解复用操作是正确的。

3 结论

本文描述了解复用电路的传统设计方法并分析了各自特点,根据2.5Gbps高速串行收发器的应用实际,采用类并行结构、基于电流模式逻辑设计了收发器的前端解复用电路,并分析了其工作原理,采用SMIC0.18um混合信号工艺完成了电路设计,并采用SpectreVerilog进行了数模混合仿真,结果表明该电路在2.5Gbps收发器电路中可以稳定可靠地工作。

- 高速ADC数字输出类型电气规格及特点(07-04)

- 12位串行A/D转换器MAX187的应用(10-06)

- AGC中频放大器设计(下)(10-07)

- 低功耗、3V工作电压、精度0.05% 的A/D变换器(10-09)

- PIC16C5X单片机睡眠状态的键唤醒方法(11-16)

- 用简化方法对高可用性系统中的电源进行数字化管理(10-02)