PCB电路设计中布线的EMC分析

摘要:PCB电路设计在生产生活中至关重要,本文从电磁兼容这一问题出发,讨论PCB电路设计,以及在设计PCB电路过程中存在的电磁干扰等问题。分析单线,多导体线和元器件的设置、路线,从而得出关于PCB电路中布线的一些设计规范和技能。如果将这些原则和规范使用于电路设计的最初环节,那么存在于布线中的电磁干扰问题就会被PCB电路设计师很快的解决。

所谓PCB(Printed Circuit Board),实际上就是印制线路板,它是一种较为重要的电子产品,是电子元器件电气连接的提供者,在电路元件与电器件之间的衔接上,起重大的作用。是电子元器件的支撑体,对电路元件和器件起支撑作用。抗干扰能力的强弱直接受印制线路板设计的优良影响。因此,线路的设置安排和抗干扰能力是设计师在设计线路时必须同时兼顾的。PCB印制线路板根据电路层数可分为单面板、双面板和多层板。常见的多层板一般为4层板或6层板,复杂的多层板可达十几层。

尽管电子工程人员经过很多年的设计与实践,已经总结出了一些规范和设计经验,但是截至目前,国家在这一方面并没有明确的要求和规则。基于此,实践中我们只能在设计电路过程中充分的运用设计原则和相关规则,进行整体规划与设计,尤其是进行电路的抗干扰设计。做到以上这些,就能有效避免电路设计实践中出现严重的电磁干扰问题,而且还能有效的降低频率和节约设计成本费用,对于有效减少电气电路设计时间具有非常重要的作用。

1 印制电路板中电磁环境的构成

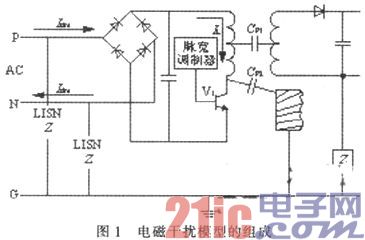

电磁干扰源,耦合途径和接收器这3个部分组成一个简单的电磁干扰模型,如图1所示。

微处理器、微控制器、静电放电、传送器以及瞬时功率执行元件都是常见的干扰源,在印制线路板中出现的频率较高。时钟电路通常情况下在一个微控制系统里是最大的宽带噪声发生器。

传导耦合和辐射耦合二者共同构成了耦合途径,在印制线路板中发挥着重要作用。耦合途径不同,产生的干扰问题也就自然不同。比如:1)互感在导线之中频频发生,同时电容处于部分状态下时,也可能会大幅度上升;2)印制板导线串扰;3)高频信号经印制导线时所产生的高频电磁场;4)因时钟信号而导致的电磁辐射干扰现象;5)反射干扰;6)因一系列操作不当产生的干扰。总之,许多物件都有可能成为敏感元件,包括电子元件和导线。要想整体把握板子的整体布局和元器件的位置就需要在布线上面下功夫,只有合理的布线和达到电磁兼容性标准才是实现这一目的最佳途径。

2 印制线路板中单根走线

PCB电路设计中,差分走线耦合较小,只占10~20%的耦合度,更多的还是对地的耦合。当地平面发生不连续时。无参考平面区域,差分走线耦合会提供回流通路。

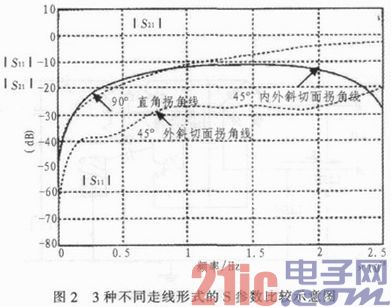

PCB布线中要求避免直角走线的出现。直角走线对信号有着负面影响,因此PCB中的走线一般采用具有45度拐角或圆弧拐角线。直角走线和非直角走线的差异主要有:1)拐角能等效为传输线上得容性负载,减少上升的时间;2)拐角也能抵御因不持续而造成的信号反射;3)电磁干扰会因直角尖端产生。

不同的拐角线,角度上具有明显的差异性。图2运用了FDTD数值方法进行试验,通过模拟对反射传输特性和反射特性这二者进行对比。在45度外斜切面拐角线反射性与传输性能上,优于其他两种拐角线。这3种走线形式比圆弧的拐角线要差,但是弧度的刻划成本比较高。这是因为圆弧的刻划要求精湛的制版技术。精湛的技术必然会引起成本的增加,因此通常在选择走线时,会将目光停留在45度外斜切面拐角线上。

3 对多导体传输线在应用中的串扰探析

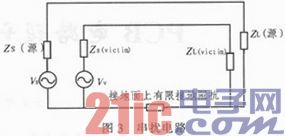

传送信号和机器的运作频率在PCB电路设计中要注意适度原则,如果达到兆赫级,那么对线路的干扰就很严重。走线间的干扰形成的主要原因是串扰问题。PCB电气电路设计过程中,应当适当地留意一下串扰问题,尽可能地减少布线串扰问题出现。实践中可以看到,若发生串扰现象,通常至少会有3个导体和两个线携带信号。如图3所示,而第3条导线只是作为一种参考而言。

实践中可以看到,源和受干扰电路之间的作用,通常会产生一种VS,该作用下的zs、zL会产生感应电压和电流,其zs和源相互联系,而zL主要与负载端相互联系。

为减少干扰现象的出现,笔者特提出以下建议和设计规划:1)以功能作为主要依据的逻辑器件,对总线结构进行控制;2)元件物理距离最小化;3)布线走线长度应严格控制;4)元件既要与I/o接口远离,又要尽可能地避开数据干扰;5)确保阻抗受控走线路径的准确性,通常频波能量较大一些的走线应当注意考虑;6)提供一些相交性的走线,以确保走线之间有适当的距离,确保电感耦合最小化;7)紧挨着的布线层应当垂直,这样

- 电源管理总线的结构与优势(11-19)

- 如何设计一个合适的系统电源(上)(11-20)

- 新型灌封式6A至12A DC-DC μModule稳压器系列(11-19)

- 如何设计一个合适的系统电源(下)(11-20)

- PCB电源供电系统的分析与设计(11-21)

- LVDS技术原理和设计简介(01-26)