用负阻原理设计高稳定度VCO

时间:08-30

来源:互联网

点击:

压控振荡器(VCO)是锁相环路的重要组成部分。随着电子技术的发展,出现了许多集成的VCO芯片。考虑到高频率稳定度、低相噪的要求,这里采用Agilent公司生产的低噪声晶体管HBFP0450来设计VCO。常用的VCO一般有三种:晶体压控振荡器、LC压控振荡器和RC压控振荡器。对于超高频段的VCO,采用LC振荡器形式;为了提高频率稳定性,采用了克拉泼电路,并进行了相角补偿。

1 负阻振荡原理

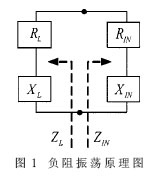

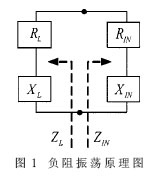

这里采用负阻方法来设计压控振荡器,负阻振荡原理图如图1所示。

图中,ZIN是晶体管电路的输入阻抗,RIN和XIN分别是输入电阻和电抗;ZL是负载阻抗,RL和XL分别是负载电阻和电抗。

根据振荡原理,起振条件是:

RIN+RL<0 (1)

振荡的平衡条件是:

RIN+RL=0 (2)

XIN+XL=0 (3)

2 设计与仿真

2.1 起振与振荡的仿真

这里用ADS来仿真电路,采用改进型克拉泼电路形式,具体电路如图2所示。选用高增益、低噪声的HBFP0450作为三端器件,它在200MHz工作频率上有20dB的增益,从而保证了较大的振荡幅度。供电电压为5V,通过R1、R2和R3来确定静态工作点,工作电流选定为10mA,Vce为2.5V。

交流等效电路如图3所示。L1、C4和C5串联可以等效成一个电感,从而满足电容三端振荡器的相位条件。L1、C4、C5、C6、C7构成了谐振回路,振荡频率主要由这五个元件所决定。频率计算公式如下:

式中,L1为线圈绕制电感,Q值为39。C为C4、C5、C6和C7串联后的等效电容,由于C4<从图4(a)的仿真结果可以看出,在200MHz附近,RIN+RL<0,所以满足起振条件,由于RIN的负阻比较大,所以提供交流能量的能力比较强,故振荡的幅度会比较大,这一点在后面的仿真和测试中可以得到证实。从图4(b)可以看出,当f为200MHz左右时,XIN+XL=0,从而满足相位平衡条件,它决定了振荡的频率。

2.2 相角补偿

三极管振荡器要满足相位平衡条件:φY+φZ+φF=2nπ(n=0,1,2,3,…)[3~4],由于φY+φF通常不等于0,所以就要求回路工作于失谐状态,以产生一个谐振回路相角φZ来对φY和φF进行平衡。也就是说,由于电路中有源器件、寄生参量以及阻隔元件等的影响,使得振荡器的实际工作频率严格来讲并不等于回路的固有谐振频率,因此,谐振回路等效阻抗ZP并不会呈现纯阻抗。所以,一般振荡器的振荡回路总是处于微小失谐状态。我们知道,并联谐振回路具有负斜率的相频特性,即δωz/δw<0,当振荡器工作在回路谐振频率上时,它对频率的稳定性能最佳。而当它工作在失谐状态时,会使得振荡器的频率稳定度与效率都降低。在此,采用相角补偿法来提高压控振荡器的频率稳定度和效率。

由参考文献可知,在集电极串入一个电感为LC=L/F的补偿元件,就可以实现相角补偿(φZ=0)。其中,L为谐振回路电感值,F为反馈系数,即F=C7/C6。L3和输出回路的C8、C9、L2可以构成等效电感LC,从而进行相角补偿,使得振荡器工作在LC回路的谐振频率上。当输出回路等效为电容时,通过实际测量,在频率214.64859MHz上的稳定度为9.3631e-4;而等效为电感时,在214.26046MHz上的稳定度为4.2278e-4。可见用等效电感进行相角补偿后,稳定度大约提高了一倍。C8、C9和L2同时构成了输出网络,对高次谐波有很好的抑制作用,并使基波输出功率平坦化。

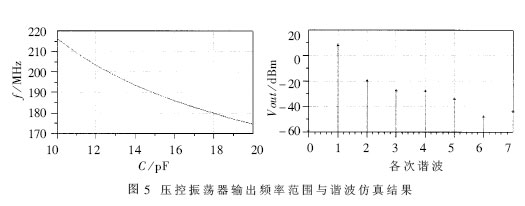

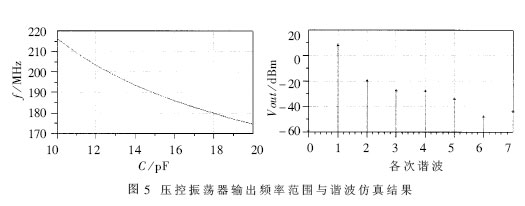

从图5可以看出,压控振荡器的输出频率范围为175MHz~217MHz,基波(频率为214MHz时)输出功率为7.911dBm,二次谐波为-16.368dBm,可见有效地抑制了谐波分量。在实际应用中,对谐波滤除的要求比较高,可以在输出端接入宽带滤波器,其电路原理图和仿真结果见图6。这样,可以更有效地滤除高次谐波,同时有利于输出匹配,减小负载对输出功率的影响。

2.3 相噪分析

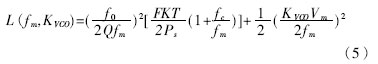

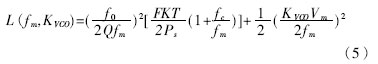

参考文献给出了LC压控振荡器的相位噪声表达式:

式中,fm为频偏,KVCO为VCO控制灵敏度,fo为振荡频率,Q为品质因数,F为晶体管的噪声系数,K为波尔兹曼常数,T为工作温度,Ps为振荡信号功率,fc为闪烁噪声拐角频率,Vm为低频噪声源的总幅度。从式(5)可以看出,选择噪声系数小的放大管、增加谐振回路有载Q值、减小VCO控制灵敏度、提高输出信号功率都可以降低相位噪声。通过减小变容管在谐振回路中的接入系数,可以有效减小VCO控制灵敏度,但是也会导致频率覆盖范围的减小,所以要适当选择接入系数。该VCO输出频率为200MHz时,变容管接入系数为0.63。通过适当调整输出回路的电感和分压电容,可以提高负载阻抗,从而有效地提高输出功率,以达到降低相位噪声的目的。通过软件仿真,在频偏10kHz处的输出相位噪声为-101.3dBc/Hz,在100kHz处的相位噪声为-122.5dBc/Hz

1 负阻振荡原理

这里采用负阻方法来设计压控振荡器,负阻振荡原理图如图1所示。

图中,ZIN是晶体管电路的输入阻抗,RIN和XIN分别是输入电阻和电抗;ZL是负载阻抗,RL和XL分别是负载电阻和电抗。

根据振荡原理,起振条件是:

RIN+RL<0 (1)

振荡的平衡条件是:

RIN+RL=0 (2)

XIN+XL=0 (3)

2 设计与仿真

2.1 起振与振荡的仿真

这里用ADS来仿真电路,采用改进型克拉泼电路形式,具体电路如图2所示。选用高增益、低噪声的HBFP0450作为三端器件,它在200MHz工作频率上有20dB的增益,从而保证了较大的振荡幅度。供电电压为5V,通过R1、R2和R3来确定静态工作点,工作电流选定为10mA,Vce为2.5V。

交流等效电路如图3所示。L1、C4和C5串联可以等效成一个电感,从而满足电容三端振荡器的相位条件。L1、C4、C5、C6、C7构成了谐振回路,振荡频率主要由这五个元件所决定。频率计算公式如下:

式中,L1为线圈绕制电感,Q值为39。C为C4、C5、C6和C7串联后的等效电容,由于C4<从图4(a)的仿真结果可以看出,在200MHz附近,RIN+RL<0,所以满足起振条件,由于RIN的负阻比较大,所以提供交流能量的能力比较强,故振荡的幅度会比较大,这一点在后面的仿真和测试中可以得到证实。从图4(b)可以看出,当f为200MHz左右时,XIN+XL=0,从而满足相位平衡条件,它决定了振荡的频率。

2.2 相角补偿

三极管振荡器要满足相位平衡条件:φY+φZ+φF=2nπ(n=0,1,2,3,…)[3~4],由于φY+φF通常不等于0,所以就要求回路工作于失谐状态,以产生一个谐振回路相角φZ来对φY和φF进行平衡。也就是说,由于电路中有源器件、寄生参量以及阻隔元件等的影响,使得振荡器的实际工作频率严格来讲并不等于回路的固有谐振频率,因此,谐振回路等效阻抗ZP并不会呈现纯阻抗。所以,一般振荡器的振荡回路总是处于微小失谐状态。我们知道,并联谐振回路具有负斜率的相频特性,即δωz/δw<0,当振荡器工作在回路谐振频率上时,它对频率的稳定性能最佳。而当它工作在失谐状态时,会使得振荡器的频率稳定度与效率都降低。在此,采用相角补偿法来提高压控振荡器的频率稳定度和效率。

由参考文献可知,在集电极串入一个电感为LC=L/F的补偿元件,就可以实现相角补偿(φZ=0)。其中,L为谐振回路电感值,F为反馈系数,即F=C7/C6。L3和输出回路的C8、C9、L2可以构成等效电感LC,从而进行相角补偿,使得振荡器工作在LC回路的谐振频率上。当输出回路等效为电容时,通过实际测量,在频率214.64859MHz上的稳定度为9.3631e-4;而等效为电感时,在214.26046MHz上的稳定度为4.2278e-4。可见用等效电感进行相角补偿后,稳定度大约提高了一倍。C8、C9和L2同时构成了输出网络,对高次谐波有很好的抑制作用,并使基波输出功率平坦化。

从图5可以看出,压控振荡器的输出频率范围为175MHz~217MHz,基波(频率为214MHz时)输出功率为7.911dBm,二次谐波为-16.368dBm,可见有效地抑制了谐波分量。在实际应用中,对谐波滤除的要求比较高,可以在输出端接入宽带滤波器,其电路原理图和仿真结果见图6。这样,可以更有效地滤除高次谐波,同时有利于输出匹配,减小负载对输出功率的影响。

2.3 相噪分析

参考文献给出了LC压控振荡器的相位噪声表达式:

式中,fm为频偏,KVCO为VCO控制灵敏度,fo为振荡频率,Q为品质因数,F为晶体管的噪声系数,K为波尔兹曼常数,T为工作温度,Ps为振荡信号功率,fc为闪烁噪声拐角频率,Vm为低频噪声源的总幅度。从式(5)可以看出,选择噪声系数小的放大管、增加谐振回路有载Q值、减小VCO控制灵敏度、提高输出信号功率都可以降低相位噪声。通过减小变容管在谐振回路中的接入系数,可以有效减小VCO控制灵敏度,但是也会导致频率覆盖范围的减小,所以要适当选择接入系数。该VCO输出频率为200MHz时,变容管接入系数为0.63。通过适当调整输出回路的电感和分压电容,可以提高负载阻抗,从而有效地提高输出功率,以达到降低相位噪声的目的。通过软件仿真,在频偏10kHz处的输出相位噪声为-101.3dBc/Hz,在100kHz处的相位噪声为-122.5dBc/Hz

振荡器 电子 电路 电阻 仿真 电压 电流 电感 电容 三极管 滤波器 相关文章:

- 一种CMOS绿色模式AC/DC控制器振荡器电路(09-16)

- 取替RC采用硅振荡器定时更胜一筹(02-17)

- 分析振荡器及天线的集成式设计(03-15)

- 智能电网增长趋势将持续,任重而道远!(02-03)

- 石英振荡器与MEMS结合的时钟器件方案(02-25)

- 反激式开关电源低电压下点亮HBLED灯(02-27)