面向信号处理与通信系统的下一代设计流程

时间:08-22

来源:互联网

点击:

- 硬件设计

在完成算法设计和系统架构后,许多开发周期的下一步是FPGA实现和数字部分的验证,有时候会作为ASIC进入最终开发。FPGA原型和实现中低效率的主要原因是耗时的设计迭代(这是寻求功耗、性能和区域达到恰当平衡所必需的)。

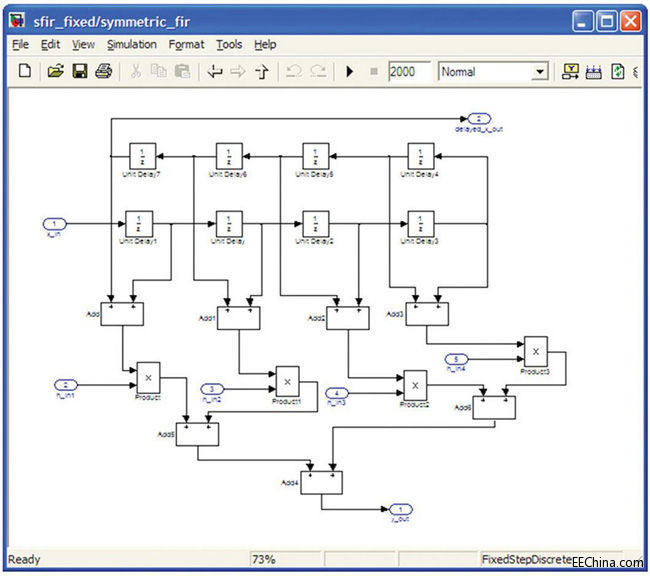

图6显示的是一个以定点算法来实现的对称FIR滤波器。为实现硬件中的滤波器,工程师必须谨慎地平衡吞吐能力和延迟,并监控所用的硬件资源量。“关键路径突出显示”是一项新功能,能针对系统中的潜在瓶颈提供可操作的信息。

图6:在Simulink中建模的对称定点FIR滤波器。

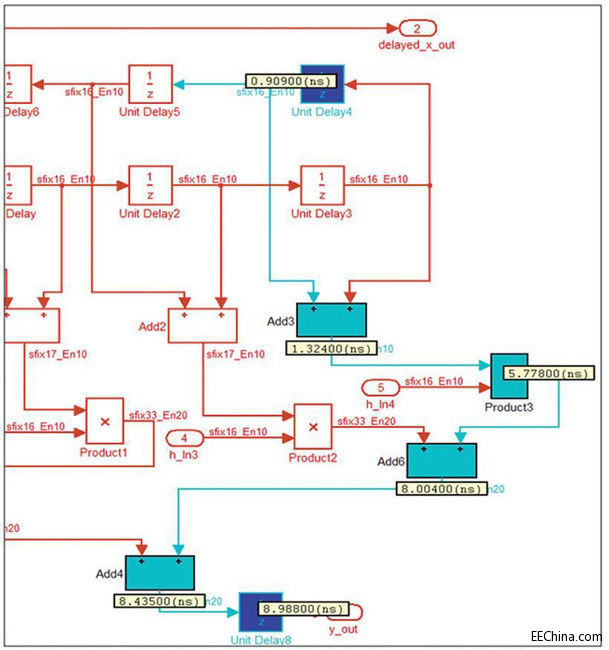

使用综合工具生成的后综合信息,HDL Coder可以在Simulink模型中对关键路径时间进行注释。工程师可以利用该信息与流水线技术,对他们的设计进行划分,以减少关键路径延迟,并推断出大部分FPGA上专用DSP可用资源的使用情况。图7展示了关键路径自动突出显示和针对每个路径段估算延迟的相同的滤波器设计。

图7:对称的定点FIR滤波器,展示关键路径和估算的延迟。

如上所述,流水线技术是工程师用来解决关键路径延迟的主要技术之一。对于流水线技术,众所周知的挑战之一是并行路径可能存在不匹配延迟,这会导致意外的系统行为。令人高兴的是,用以解决这一问题的分布式流水线技术现在已实现了自动化。通过选择该方案,工程师可以自动重定时模型,并在相关的并行路径中平衡流水线寄存器所引入的延迟。

在过去,这些类型的设计迭代和权衡评估要求我们投入大量的时间和精力。最近,包括Workflow Advisor控制台在内的增强,使工程师能够以直观的方式更快地完成设计迭代。对于那些不是特别熟悉HDL编程却需要利用FPGA处理的人员来说,这特别有帮助。

除了使用关键路径突出显示和分布式流水线技术外,工程师还可以查看一份自动生成的资源使用报告,来监控所用的关键硬件组件的类型和数量,并通过对多个可行的设计方案进行快速迭代,为给定的情况确定最佳架构选择。

加速跨团队的设计

今天的工程经理面临协调处理整个系统不同部分的团队的挑战,这些团队位于不同地方、使用不同的工具。在许多情况下,系统级设计最好在图形环境中完成,而某些较低级别的细节设计最好在MATLAB或C中最好以文本的形式表示。本文展示了一些提升跨设计流程各个阶段的效率的最新技术发展。

对于算法设计,在建模、仿真信号处理,以及通信系统中,System对象库是一个重要的新开发工具。现在,MATLAB中可提供数百个即用型信号处理与通信System对象。此外,System对象支持定点算法,它们可以与Simulink集成或用于自动生成C代码。SimRF采用电路包络仿真技术,是面向更高效系统架构流程的重要新工具。它使工程师可以在一个统一的环境中对RF和基带系统组件进行建模,并执行真正的多频仿真。

为了缩短硬件设计的设计迭代循环时间,HDL Coder中有多个最新的开发工具,包括Workflow Advisor、关键路径突出显示、分布式流水线技术、回注及资源利用情况报告,这提供了有关系统性能的可操作信息,并为硬件开发人员简化工作流框架。

无论团队是小是大,地理位置分散还是位于同一个办公室,工程部门可以应用部分这些技术来消除其工作流程中的不连续,并借此简化和加速复杂信号处理与通信系统的开发。

仿真 DSP 编码器 LTE 蓝牙 ZigBee 收发器 电路 放大器 振荡器 FPGA 滤波器 自动化 相关文章:

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 数字频率合成器的FPGA实现(08-07)

- 基于DSP的导弹仿真器嵌入式组件设计(04-30)

- 如何将DSP和MCU两者完美结合(08-10)

- 高性能仿真器与开发包加速普及DSP应用开发(11-22)

- 基于DSP内嵌PCI总线的卫星信号仿真器设计(04-17)