例说FPGA连载61:电子点菜单之FIFO概述

时间:12-23

来源:互联网

点击:

例说FPGA连载61:电子点菜单之FIFO概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

所谓FIFO(First In First Out),即先入先出,这是一种典型的计算机数据或指令处理机制,和中国人所谓的“先来后到”理念有异曲同工之妙。而我们这里要说的FIFO存储器,和前面带有地址可直接定位操作的ROM或RAM存储器不同,FIFO存储器没有地址定义;那你可能会认为FIFO存储器和上一节的移位寄存器差不多,还真“差不多”,但是FIFO存储器的输出可要比移位寄存器来得灵活,移位寄存器只要存储深度固定,基本上只能在存储器被“填满”或有固定个数的数据字节被“填满”时我们才能够读出或输出数据,而FIFO存储器则一旦有数据写入或输入,随时都可以在读出或输出端进行操作,获得数据。

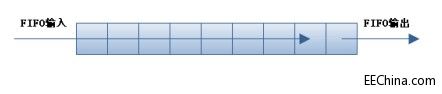

如图10.5所示,FIFO存储器内部我们可以简单的认为就是一条整齐划一的“队列”,操作起来就是一个挨着一个,并且井然有序。FIFO存储器的机理虽然简单,但是作用却异常强大,在多芯片数据交换传输的应用中,往往都会让FIFO存储器来做承前启后的“缓冲器”。

图10.5 FIFO工作原理图示意图

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)