例说FPGA连载56:VGA显示驱动之复用引脚设置

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

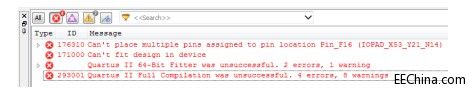

在该实例中,SF-VGA子板连接到VIP核心板的插座P4。在分配好引脚后,若直接进行编译,则将会出现如图7.6所示的错误。

图7.6 引脚复位错误报告

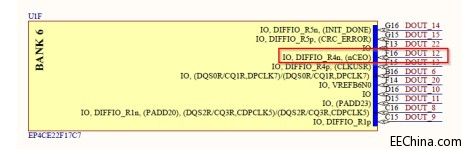

这是怎么回事?为什么Pin_F16有“multiple pins assigned to”,即多个信号分配给这个引脚?如图7.7所示,pin assignment中并没有多个信号分配给Pin_F16这个引脚,只有adv7123_sync_n分配给了它。

图7.7 引脚分配

再来看看如图7.8的原理图,这里的F16引脚,FPGA的功能定义是“IO, DIFFIO_R4n, (nCEO)”。问题就在这个“nCEO”上,这是个配置相关的引脚,默认情况下Quartus II工具认为它作为配置功能使用,如果用户将它分配到信号上,则编译时必定报错。

图7.8 FPGA原理图

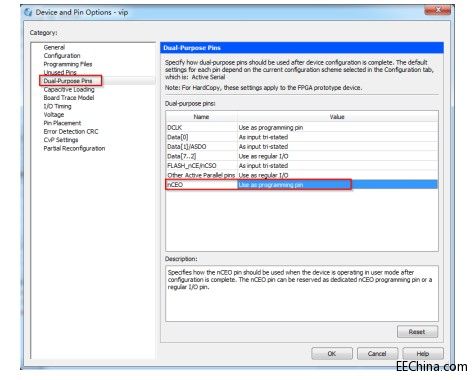

那么这个错误如何规避?很简单,大家在Quartus II菜单中点击“Assignments à Device…”,进入Device界面如图7.9所示。找到“Device and Pin Options…”按钮,单击它。

图7.9 Device选项卡

如图7.10所示,在“Category”下面选择“Dual-Purpose Pins”,然后找到右侧的“nCEO”一栏,默认的设置是“Use as programming pin”。双击它,将它改为“Use as regular I/O”。

图7.10 Device and Pin Option选项卡

重新编译工程,不会再有错误信息。同样的,如果使用“Dual-Purpose Pins”遇到类似的问题,可以通过类似的方式解决。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)