例说FPGA连载68:AV视频采集之移位寄存器时序解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

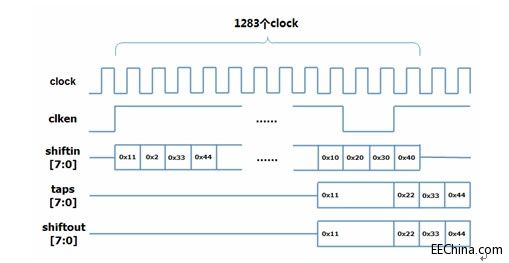

下面我们给出几个时序波形图,帮助大家来理解移位寄存器接口的工作原理。如图12.16所示,这里假设移位寄存器原本是空的,我们在clken拉高时,从shiftin[7:0]连续输入了1283个数据,那么在输入数据的第1280个时钟周期,即图示的clken拉高的倒数第4个时钟周期(对应shift[7:0]的数据为0x10时),taps[7:0]和shiftout[7:0]同时出现了移位寄存器在1280个时钟周期前由shiftin[7:0]接口输入的数据,即0x11。以此类推,随后若clken继续保持高电平,则taps[7:0]和shiftout[7:0]总线上将持续输出由shiftin[7:0]输入的数据。

图12.16 移位寄存器工作原理波形示意图1

我们接着来看,若clken在某些时钟周期拉低,则会出现什么情况。如图12.17所示,clken在拉高了1280个时钟周期后,紧接着拉低2个时钟周期,然后再拉高。那么,在第1280个时钟周期,taps[7:0]和shiftout[7:0]总线上正常出现1280个时钟周期前在shiftin[7:0]上的数据。而紧接着的2个clken拉低的时钟周期里,taps[7:0]和shiftout[7:0]总线是的数据保持0x11不变,只有当clken再次拉高后,它们才会继续更新输出的数据。也就是说,clken拉低的时钟周期里,移位寄存器内部相当于停滞状态。利用这个特性,其实可以帮助我们设计中在使用移位寄存器时实现一些灵活的数据流控制。

图12.17移位寄存器工作原理波形示意图2

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)