例说FPGA连载54:NAND Flash实例之Avalon-ST总线

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

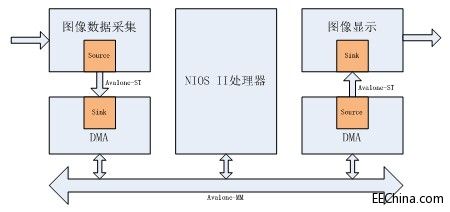

相对于Avalon-MM总线基于地址映射的访问方式,Avalon-ST总线更适合于高带宽、低时延的单向数据流传输。举个实例来说,如图6.12所示,对于一个简单的图像采集显示系统,在衔接一些高数据吞吐量的接口上就可以让Avalon-ST总线派上用场。假设这个实例系统中NIOS II处理器负责将前端采集的图像进行解码或是其他处理,然后再送给显示终端。那么在图像采集的前端就会产生大量的数据吞吐量,而在图像显示刷新的后端也会有大量的数据搬运工作,那么这些任务交给Avalon-ST并且配合DMA来搞定最合适不过了。

图6.12 图像采集显示系统

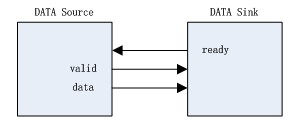

我们同样可以用一个最简单的Avalon-ST接口来领会其工作原理,如图6.13所示。在这个Avalon-ST的源端(source)和宿端(sink)之间只用了2个控制信号valid和ready就可以轻松完成单向数据流data的传输。其实这样简单的传输控制方式我们在逻辑设计中也是非常频繁的用到,但是若深入研究Avalon-ST总线的一整套传输机制,那可还真是有学问。

图6.13 Avalon-ST接口

通信的机理也蛮简单的,ready信号用于指示数据宿(DATA Sink)端是否准备就绪,是否可以接受数据源(DATA Source)端传输过来的数据信号data。而数据源端在需要发送数据的时候也会先检查ready信号是否处于有效状态,若是有效,则拉高valid使之有效,同时将需要传输的数据赋给数据信号data。数据宿端根据valid信号的有效与否决定是否接收当前的数据。当然,这里省略了时钟信号,每次数据传送通常都是按照时钟信号一个节拍一个节拍的工作。

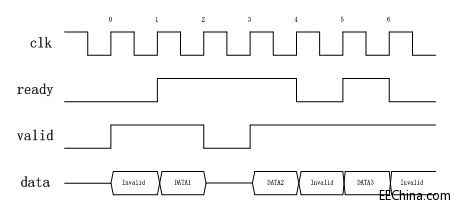

如图6.14所示,对于这个简单的Avalon-ST总线传输而言,在宿端拉高ready信号以后源端发送过来的数据(valid有效时)才会被接收。图中的clk0时刻valid信号有效,但是ready信号无效,所以此时传输的数据无效(Invalid);clk1时刻valid信号和ready同时有效,那么数据DATA1就能被宿端接收;clk2时刻valid无效则不锁存任何数据;clk3时刻DATA2被锁存;clk4时刻由于ready信号无效则传输数据无效;后续依次类推。

图6.14 Avalon-ST总线传输时序波形

简单的接口模型和示意图让我们看清了Avalon-ST总线的本来面目,在实践中应用Avalon-ST总线也就不再困难。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)