例说FPGA连载46:Qsys系统搭建与软件开发之功能概述

时间:11-14

来源:互联网

点击:

例说FPGA连载46:Qsys系统搭建与软件开发之功能概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

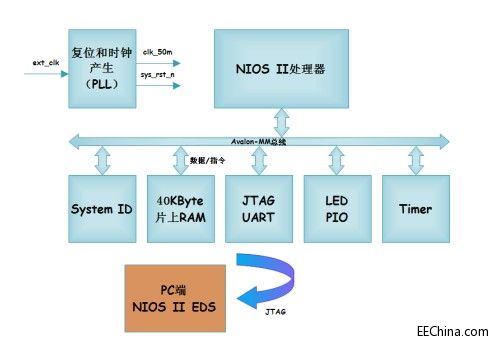

如图5.1所示,本实例使用Quartus II的Qsys评估构建一个片上系统。这个系统有NIOS II处理器,它的代码和数据都是存储在40Kbyte的片上RAM中运行的。此外,还有一些常见外设如System ID、JTAG UART、LED PIO和Timer(定时器)。JTAG UART使用PC和VIP核心板之间的JTAG连接进行数据传输,在系统调试中非常实用。

本实例搭建好一个最基本的嵌入式处理器硬件平台后,将编写一个最简单的LED闪烁的软件程序运行在NIOS II处理器上。

图5.1工程实例3功能框图

本实例的软件流程图如图5.2所示。程序运行后,首先会进入后台进行相关外设的初始化操作,这个步骤在我们编写的应用软件上是看不到的。接着通过JTAG UART在EDS(NIOS II处理器的软件开发工具)上打印一串字符,最后进入while循环中进行LED指示灯闪烁控制。

图5.2工程实例3软件流程图

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)