例说FPGA连载44:DDR控制器集成与读写测试之Verilog代码解析

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

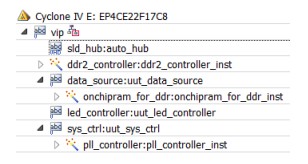

本实例有8个模块,3个层级。其层次结构如图4.22所示。

图4.22 代码层次图

● vip.v是顶层模块,其下例化了5个子模块,即sld_hub.vhd模块、ddr2_controller.v模块、data_source.v模块、onchipram_for_ddr.v模块、led_controller.v模块和sys_ctrl.v模块。该模块仅仅用于子模块间的接口连接,以及和FPGA外部的接口定义,该模块中未作任何的逻辑处理。

● sld_hub.vhd二级子模块是一个软核IP,编译时自动产生,不是我们在顶层代码vip.v中例化的。它用于我们FPGA的片内RAM和Quartus II之间通过JTAG进行数据交互。换句话说,这个模块其实是一个JTAG协议的接口实现模块。该模块是VHDL编写,并且内部代码对用户是一个“黑盒”,我们只要会使用它就可以,无需关心它的代码内容。

● ddr2_controller.v二级子模块也是一个软核IP,实现DDR2的时序控制功能,并且通过一个简单的Avalon接口实现DDR2和FPGA逻辑之间的读写数据传输。其实该模块下还有多个子模块,但由于只是一个IP核,内部代码不直接开放,所以我们姑且认为它是我们工程中的一个模块。

● data_source.v二级子模块是用户逻辑,我们用它定时产生一组写入DDR2地址0-1023的连续的有规律的数据;并且我们也会定时的读出DDR2地址0-1023地址的数据,将这些数据再写入到FPGA例化的片内RAM里。

● onchipram_for_ddr.v三级子模块是硬核IP,它例化实现了FPGA的一块片内RAM空间。

● sys_ctrl.v二级子模块中例化了PLL模块,并且对输入PLL的复位信号以及PLL锁定后的复位信号进行“异步复位,同步释放”的处理,确保系统的复位信号稳定可靠。

● pll_controller.v三级子模块为FPGA器件特有的IP硬核模块,其主要功能是产生多个特定输入时钟的分频、倍频、相位调整后的输出时钟信号。

● led_controller.v二级子模块进行24位计数器的循环计数,产生分频信号用于实现LED指示灯的闪烁。

FPGA Verilog Quartus VHDL LED 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)