例说FPGA连载43:DDR控制器集成与读写测试之DDR2引脚电平设置

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

DDR2的标准IO电平不是我们接触最多的3.3V TTL,而是1.8V的“SSTL-18 Class I”标准,那么这个电平标准,在FPGA中如何设置?

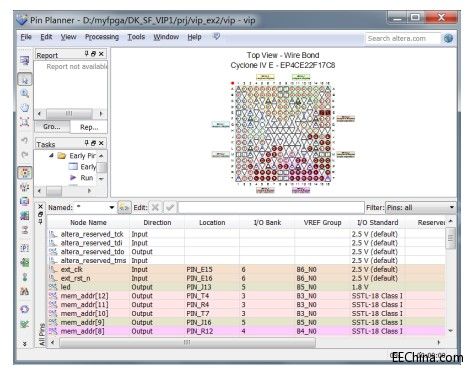

我们可以先点击Quartus II的菜单“Assignments à Pin Planner”,打开Pin Planner如图4.18所示。这里可以做FPGA信号和实际芯片die引脚的映射,包括引脚的电平标准、电流强度、片内上下拉、偏斜率等等参数都可以在这里配置。这种灵活的引脚可配置性,其实也是FPGA可编程灵活性的一大体现。

图4.18 Pin Planner界面

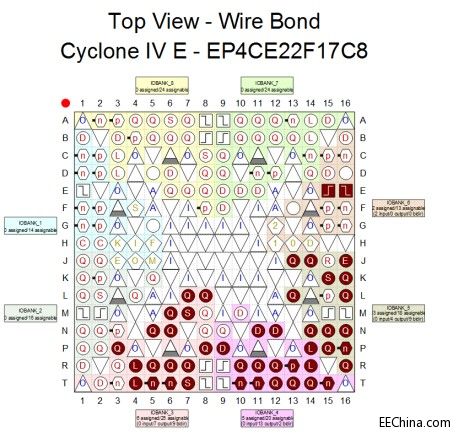

在这个Pin Planner界面中,我们可以先看看“Top View – Wire Bond”这个视图。如图4.19所示,在芯片引脚视图的外侧,有8个小矩形框分别标示了IO BANK号,图中对应不同的颜色表示了不同的IO BANK。

图4.18 引脚视图

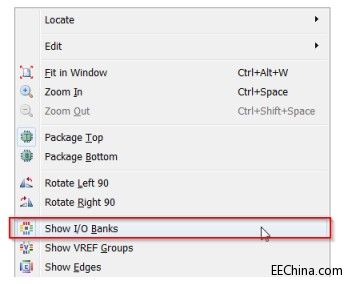

若是“Top View – Wire Bond”没有出现不同的IO BANK标示,那么我们可以在这个视图的空白处点击右键,如图4.19所示,然后单击“Show I/O Banks”选项打开。

图4.19 引脚视图的右键菜单

FPGA的电平标准,通常是以IO BANK为单位进行划分的,对于一颗FPGA芯片,它通常会根据实际情况,将一些就近的引脚划分在同一个IO BANK中,并且一颗FPGA芯片总会或多或少划分出几个IO BANK来。不同的IO BANK可以有不同的IO电平标准,但是在同一个IO BANK内的引脚,它们的IO电平标准一定是一样的。

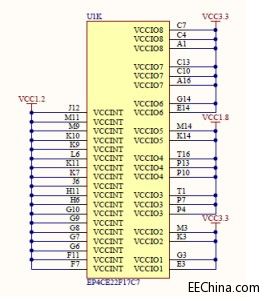

回到我们的应用中来,在我们的核心板上,大都是的IO BANK的电平都是3.3V的,而DDR2引脚所使用的IO BANK则是1.8V。如图4.20所示,在原理图设计上,VCCIO电压供1.8V的BANK3、BANK4和BANK5,都连接了DDR2的引脚。

图4.20 FPGA供电电路

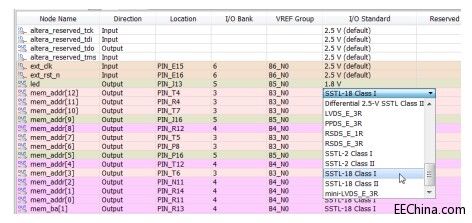

基于此,我们在FPGA内部的引脚电平标准的设定上,我们也需要做相应的设定。如图4.21所示,我们在“I/O Standard”一列中,对应DDR2引脚,选择它们的电平标准为“SSTL-18 Class I”。

图4.21 DDR2引脚电平设置

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)