例说FPGA连载19:DDR2电路设计

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

FPGA通常有专用的接口支持诸如DDR2、DDR3等高速的存储器,因此在对其引脚进行连接时,需要使用FPGA定义好的专用存储器接口总线,不能随心所意的随意连接。Altera公司的FPGA器件,在它们的官方网站上都可以下载到与器件对应的引脚定义文档(通常有excel格式、txt格式或pdf格式),在这些文档中,详细的罗列了哪些引脚可以用于存储器数据总线、地址总线、时钟或控制信号的连接。因此,在着手设计前,一定要先参考并定义好FPGA于存储器间的接口连接。

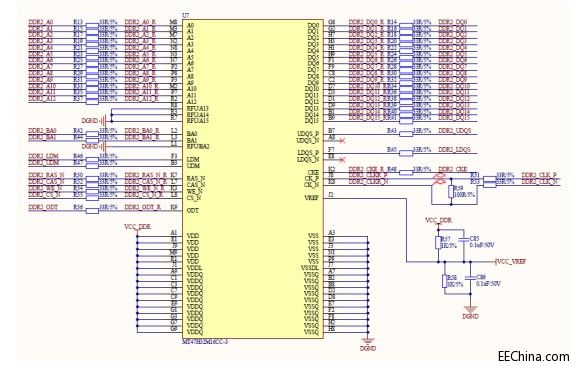

DDR2芯片的连接电路如图2.27所示。

图2.27 DDR2芯片接口电路

DDR2芯片接口以及PCB layout,通常需要遵循以下的原则。

● 单端信号的电路板阻抗一般控制在50 ohm ± 10%;差分信号的电路板阻抗一般控制在100 ohm ± 10%。

● DQ, DQS, CK/CK#选择VSS作为参考平面;地址、命令、控制信号线选择VDD作为参考平面。

● 双向I/O,如DQ,串行端接电阻放置在走线的中间,用于抑制振铃、过冲和下冲。

● 单向信号,如地址、控制和命令线,串行端接电阻放置在走线的中间或信号的发送端,推荐放在信号的发送端。

● 推荐的线宽为:

信号名 | 最小线宽 | 标准线宽 |

DQ、DQS、地址、控制、命令信号 | 4mils | 6mils |

时钟线 | 4mils | 6~10mils |

● 推荐的线间距

信号名 | 最小间距 | 标准间距 | 最大间距 |

DQ和DQ之间 | 8mils | 12mils |

|

DQ和DQS之间 | 8mils | 12mils |

|

DQ和DM之间 | 8mils | 12mils |

|

地址和地址线之间 | 6mils | 12mils |

|

CAS#,RAS#,WE#,CS#,CKE | 6mils | 15mils |

|

CK和CK#之间 | 4mils |

| 6mils |

CK/CK#与其他信号之间 |

| 20mils |

|

● DQS一般布线在DQ信号组的中间。

● DQS与时钟信号线不相邻。

● 为了避免串扰,数据信号组和地址、控制、命令信号组之间的走线间距至少+-20mils,建议它们在不同的信号层走线。

● 时钟信号组尽量走在内层,CK和CK#的走线长度偏差在+-20mils以内,最好是+-10mils以内。

● 数据信号组的走线长度和时钟信号组的走线长度偏差在+-500mils以内。

● 同一组信号线的走线长度偏差在+-50mils(+-25mils)以内。

● 地址、命令、控制信号线的走线长度与时钟信号组的走线长度偏差在+-400mils以内。

● 同一地址、命令、控制信号组内的走线长度偏差在+-50mils。

● 所有信号走线长度控制在2000mils(50mm)内。

● VREF布局布线:

n VREF和其他信号之间保持20mm间距。

n VDD到VREF的走线尽可能短。

n 去耦电容尽可能靠近VREF。

n VREF走线至少20~25mils。

n VREF和相邻走线之间至少保持15~25mils间距。

● 布线顺序:

n 数据信号DQ,DQS,DM

n 地址信号,命令信号CAS#,RAS#,WE#

n 控制信号CS#,CKE

n 时钟信号

n 反馈信号

● 蛇形走线相邻走线间距是线宽的5倍。

图2.28 蛇形走线线宽与间距的关系

FPGA 电路 总线 Altera PCB 电阻 电容 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)