例说FPGA连载25:CMOS摄像头子板设计

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

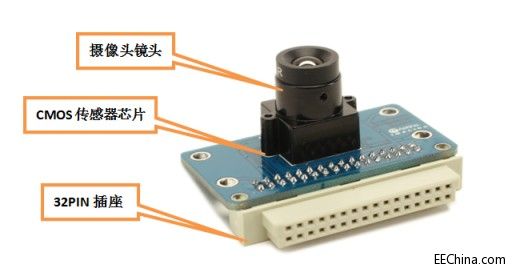

SF-MT9D111子板的实物照片如图2.43所示。

图2.43 SF-MT9D111子板实物照片

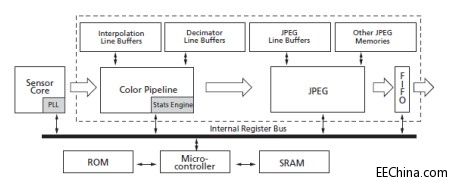

SF-MT9D111子板上板载美光的CMOS摄像头MT9D111,它是美光的一款在单芯片系统上集成了一个先进的200万像素图像传感器和功能强大的图像处理技术芯片。单芯片系统中的自动特性可以调整各种参数,以便在各种光照条件下拍摄到优质图像。MT9D111也可以简化设计工程师的工作,因为所有的处理功能、内存以及与镜头的接口都集成在一个单传感器处理芯片上。 MT9D111是一颗1/3英寸、200万像素的CMOS图像传感器,它自带有集成的先进相机系统。此相机系统包含一个复杂的图像流处理器(IFP)、一个实时JPEG编码器、一个集成的微控制器、闪光控制、自动聚焦、光学缩放以及机械快门。整个系统级芯片(SoC)可以在低照度条件下具备卓越的性能,同时功耗很低。MT9D111的内部功能框图如图2.44所示。

图2.44 MT9D111芯片内部功能框图

SF-MT9D111子板的主要接口定义如表2.6所示。

表2.6 SF-MT9D111子板连接引脚定义

名称 | 位置 | 功能描述 |

SCL | P1-7 | IIC配置时钟信号。 |

SDA | P1-8 | IIC配置数据信号。 |

PCLK | P1-11 | 视频输出时钟同步信号。 |

VSYNC | P1-13 | 视频输出场同步信号。 |

HSYNC | P1-14 | 视频输出行同步信号。 |

MCLK | P1-16 | MT9D111的时钟输入。 |

VD0 | P1-24 | 视频输出数据总线。 |

VD1 | P1-23 | 视频输出数据总线。 |

VD2 | P1-22 | 视频输出数据总线。 |

VD3 | P1-21 | 视频输出数据总线。 |

VD4 | P1-20 | 视频输出数据总线。 |

VD5 | P1-19 | 视频输出数据总线。 |

VD6 | P1-18 | 视频输出数据总线。 |

VD7 | P1-17 | 视频输出数据总线。 |

FPGA CMOS 传感器 编码器 SoC 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)