SDSoC开发环境能为您带来什么?

时间:04-13

来源:互联网

点击:

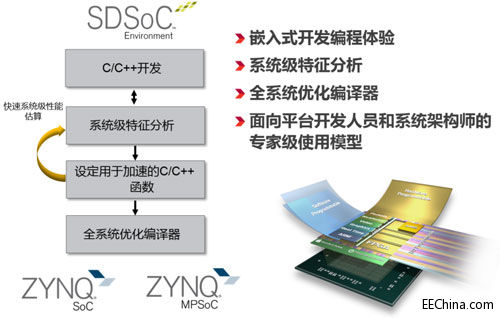

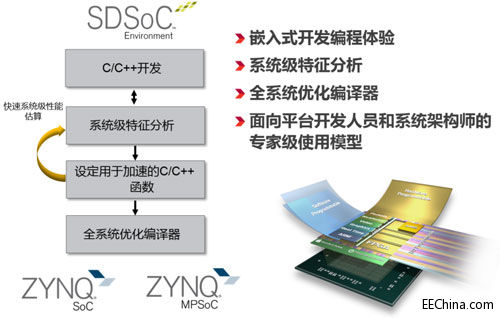

SDSoC开发环境的优势

SDSoC提供给用户的是一个可以用来完成整个Zynq SoC和MPSoC开发的基于Eclipse的软件环境,这个环境对那些已经在使用DSP芯片、视频SoC 和CPU处理器的嵌入式开发人员来说是在熟悉不过的。

在IDE中,用户可以简单地选择用来放入PL中加速的功能块,无需手动创建用于硬件实现的Vivado工程或是软件驱动程序。另外,已经有很多针对FPGA硬件优化过的IP库可以经由Vivado HLS导出,除了赛灵思和ARM,我们也有很多合作伙伴提供更多特定的算法库,包括视频类,加解密,OpenCV等等。帮助用户进一步提高生产力。

关于操作系统,目前的SDSoC版本中已经支持的目标平台Platform大都支持多种OS,包括Linux,FreeRTOS和Standalone,如果用户需要其他操作系统的支持,只要将所需OS打包到所用的目标平台中即可。具体做法涉及SDSoC目标平台的创建,我们稍后会在另外的文章中做详细介绍。

SDSoC提供系统级特征分析功能。包括快速的性能估算,允许用户通过快速的性能反馈来调整和优化软硬件代码分区、调整系统构建,从而达到系统要求的性能和面积,同时为整个开发过程节省了大量时间。这个估算是对整个系统的性能估算,包括可编程逻辑、数据通信和处理器系统等,SDSoC还可以报告出部分功能块加速后的软件/硬件的周期性能、可编程逻辑部分的硬件占用率。SDSoC也可以通过在ARM上的快速运行反馈来报告出全软件实现方案的周期性能,同时跟硬件加速方案性能估算进行对比,快速报告出性能提升比例。帮助用户在最短的时间内探索出最佳的设计实现方案。

在目标平台上运行时,SDSoC还可以通过使用ARM 处理器提供的性能计数器和自动插入到可编程逻辑的AXI总线性能监视器即APM来收集包括自动化高速缓存,内存和总线利用率等等的硬件性能数据,报告系统性能测量数据。

SDSoC的核心技术可谓业界首创的全系统优化编译器,这个编译器是一个统一的界面,不仅可以针对基于ARM的处理器系统,也可以针对片内的可编程逻辑。SDSoC开发环境旨在为系统架构师以及软件开发团队提供一个可以使用唯一的“黄金C / C ++代码”来快速配置,并同步生成构建系统所需的各类软硬件架构的可能。软硬件统一的编译器,可以从系统视角出发,带来最佳的系统构建与连接,优化的存储器接口和软件驱动等。全系统优化编译器的另一大优势是支持快速的设计空间探索,允许开发者在性能和吞吐量,延迟及面积之间作出权衡,同时保持较短的设计迭代次数。

具体到提升设计生产力这一点来说,我们就以一个32乘32 的浮点矩阵乘法设计来举例,如上图所示,正因为SDSoC开发环境特有的全系统优化编译器和系统级特征分析等功能,使得使用SDSoC进行设计后,用户可以在很短的时间内迅速生成系统配置和各种宏观、微观架构,探索最佳的互联和存储器接口,从而使得用户可以在最短的时间内探索出使用Zynq SoC设计的十几种可能的配置,并找到其中性能最佳的组合(图中用绿色圈出),继而继续使用SDSoC来具体进行设计实现和调试。

配合使用ARM 处理器提供的性能计数器和自动插入到可编程逻辑的AXI总线性能监视器收集到的各种性能数据,SDSoC还可以帮助系统架构师在最短的时间内探索出针对自己的应用平台和设计应用来说性能最佳的系统设计方案。与传统的软件硬件分别开发的流程相比可以节约大量的开发时间和成本。

SDSoC应用示例

介绍了这么多SDSoC的优势,相信不难看出,SDSoC提供的是一个真正的端到端流程。对用户来说,从C/C++代码入手,经过SDSoC,可以完成软硬件分区,生成RTL IP功能块,完成PS和PL之间的功能连接,包括硬件接口和软件驱动,最后针对目标设计平台产生出可以用来加载FPGA的比特流文件和可以用来启动操作系统的软件引导映像。所有这些在以往需要多个部门通力合作的工序如今都已经简化到SDSoC这一个开发环境中。

这里我们要强调一下,虽然对用户来说,整个图形化操作界面是软件和嵌入式开发人员非常熟悉的,所有的工序也都是在SDSoC这一个开发环境中执行和实现。但SDSoC并不是完全独立完成了包括估算、编译、调试和配置等等的过程,真正完成这些工序的仍然是在后台被SDSoC自动调用的各种赛灵思已经成熟商用的软件,包括Vivado、HLS、IPI和SDK等等。

换句话说,SDSoC的问世并不是为了替代在它之前已经用于Zynq SoC开发的各个独立的工具,而是将其整合在一起,并提供全系统编译和特征分析。是提升SoC开发的设计效率和生产力的一大利器。

下面我们来看一个简单的示例:

首先,所有算法输入可以都是由C/C++写成,或是有部分为Vivado HLS生成的IP,甚至可以就是由HDL写成的IP,只要将其设为C语言可调用IP即可。 主函数下面包含一个矩阵乘法,和一个矩阵加法。SDSoC读入设计的源代码,我们选择将矩阵乘法和加法在PL中加速,而主函数仍然留在PS中运行。要实现这样的软硬件分区,用户仅需在SDSoC中选择需要硬件加速的功能函数并指定即可。SDSoC会根据用户的划分来生成PS和PL之间的DataMover、配置硬件接口和软件驱动,输出成Vivado IPI工程,同时提供全系统性能分析和估算。用户可以根据需要对系统实现方式进行干预和改动。最后,SDSoC可以输出整个设计的FPGA比特流文件和可以用来启动操作系统的软件引导映像。

这一过程全部都在SDSoC的界面中完成,并且可以在短短数个小时内探索多个系统配置方案,找到相对最佳性能的实现方案,并加载到目标板上进行调试和验证。放在以往软硬件分别设计的传统流程上简直不可想象。

SDSoC提供给用户的是一个可以用来完成整个Zynq SoC和MPSoC开发的基于Eclipse的软件环境,这个环境对那些已经在使用DSP芯片、视频SoC 和CPU处理器的嵌入式开发人员来说是在熟悉不过的。

在IDE中,用户可以简单地选择用来放入PL中加速的功能块,无需手动创建用于硬件实现的Vivado工程或是软件驱动程序。另外,已经有很多针对FPGA硬件优化过的IP库可以经由Vivado HLS导出,除了赛灵思和ARM,我们也有很多合作伙伴提供更多特定的算法库,包括视频类,加解密,OpenCV等等。帮助用户进一步提高生产力。

关于操作系统,目前的SDSoC版本中已经支持的目标平台Platform大都支持多种OS,包括Linux,FreeRTOS和Standalone,如果用户需要其他操作系统的支持,只要将所需OS打包到所用的目标平台中即可。具体做法涉及SDSoC目标平台的创建,我们稍后会在另外的文章中做详细介绍。

SDSoC提供系统级特征分析功能。包括快速的性能估算,允许用户通过快速的性能反馈来调整和优化软硬件代码分区、调整系统构建,从而达到系统要求的性能和面积,同时为整个开发过程节省了大量时间。这个估算是对整个系统的性能估算,包括可编程逻辑、数据通信和处理器系统等,SDSoC还可以报告出部分功能块加速后的软件/硬件的周期性能、可编程逻辑部分的硬件占用率。SDSoC也可以通过在ARM上的快速运行反馈来报告出全软件实现方案的周期性能,同时跟硬件加速方案性能估算进行对比,快速报告出性能提升比例。帮助用户在最短的时间内探索出最佳的设计实现方案。

在目标平台上运行时,SDSoC还可以通过使用ARM 处理器提供的性能计数器和自动插入到可编程逻辑的AXI总线性能监视器即APM来收集包括自动化高速缓存,内存和总线利用率等等的硬件性能数据,报告系统性能测量数据。

SDSoC的核心技术可谓业界首创的全系统优化编译器,这个编译器是一个统一的界面,不仅可以针对基于ARM的处理器系统,也可以针对片内的可编程逻辑。SDSoC开发环境旨在为系统架构师以及软件开发团队提供一个可以使用唯一的“黄金C / C ++代码”来快速配置,并同步生成构建系统所需的各类软硬件架构的可能。软硬件统一的编译器,可以从系统视角出发,带来最佳的系统构建与连接,优化的存储器接口和软件驱动等。全系统优化编译器的另一大优势是支持快速的设计空间探索,允许开发者在性能和吞吐量,延迟及面积之间作出权衡,同时保持较短的设计迭代次数。

具体到提升设计生产力这一点来说,我们就以一个32乘32 的浮点矩阵乘法设计来举例,如上图所示,正因为SDSoC开发环境特有的全系统优化编译器和系统级特征分析等功能,使得使用SDSoC进行设计后,用户可以在很短的时间内迅速生成系统配置和各种宏观、微观架构,探索最佳的互联和存储器接口,从而使得用户可以在最短的时间内探索出使用Zynq SoC设计的十几种可能的配置,并找到其中性能最佳的组合(图中用绿色圈出),继而继续使用SDSoC来具体进行设计实现和调试。

配合使用ARM 处理器提供的性能计数器和自动插入到可编程逻辑的AXI总线性能监视器收集到的各种性能数据,SDSoC还可以帮助系统架构师在最短的时间内探索出针对自己的应用平台和设计应用来说性能最佳的系统设计方案。与传统的软件硬件分别开发的流程相比可以节约大量的开发时间和成本。

SDSoC应用示例

介绍了这么多SDSoC的优势,相信不难看出,SDSoC提供的是一个真正的端到端流程。对用户来说,从C/C++代码入手,经过SDSoC,可以完成软硬件分区,生成RTL IP功能块,完成PS和PL之间的功能连接,包括硬件接口和软件驱动,最后针对目标设计平台产生出可以用来加载FPGA的比特流文件和可以用来启动操作系统的软件引导映像。所有这些在以往需要多个部门通力合作的工序如今都已经简化到SDSoC这一个开发环境中。

这里我们要强调一下,虽然对用户来说,整个图形化操作界面是软件和嵌入式开发人员非常熟悉的,所有的工序也都是在SDSoC这一个开发环境中执行和实现。但SDSoC并不是完全独立完成了包括估算、编译、调试和配置等等的过程,真正完成这些工序的仍然是在后台被SDSoC自动调用的各种赛灵思已经成熟商用的软件,包括Vivado、HLS、IPI和SDK等等。

换句话说,SDSoC的问世并不是为了替代在它之前已经用于Zynq SoC开发的各个独立的工具,而是将其整合在一起,并提供全系统编译和特征分析。是提升SoC开发的设计效率和生产力的一大利器。

下面我们来看一个简单的示例:

首先,所有算法输入可以都是由C/C++写成,或是有部分为Vivado HLS生成的IP,甚至可以就是由HDL写成的IP,只要将其设为C语言可调用IP即可。 主函数下面包含一个矩阵乘法,和一个矩阵加法。SDSoC读入设计的源代码,我们选择将矩阵乘法和加法在PL中加速,而主函数仍然留在PS中运行。要实现这样的软硬件分区,用户仅需在SDSoC中选择需要硬件加速的功能函数并指定即可。SDSoC会根据用户的划分来生成PS和PL之间的DataMover、配置硬件接口和软件驱动,输出成Vivado IPI工程,同时提供全系统性能分析和估算。用户可以根据需要对系统实现方式进行干预和改动。最后,SDSoC可以输出整个设计的FPGA比特流文件和可以用来启动操作系统的软件引导映像。

这一过程全部都在SDSoC的界面中完成,并且可以在短短数个小时内探索多个系统配置方案,找到相对最佳性能的实现方案,并加载到目标板上进行调试和验证。放在以往软硬件分别设计的传统流程上简直不可想象。

赛灵思 Xilinx FPGA ARM SoC 嵌入式 PSoC 仿真 DSP C语言 VHDL Verilog 总线 Linux 自动化 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)