零基础学FPGA(八)手把手解析时序逻辑乘法器代码

时间:02-25

来源:互联网

点击:

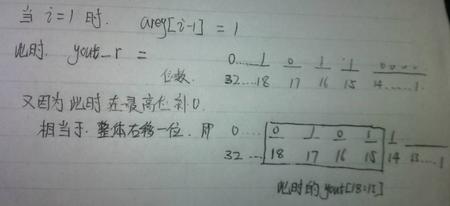

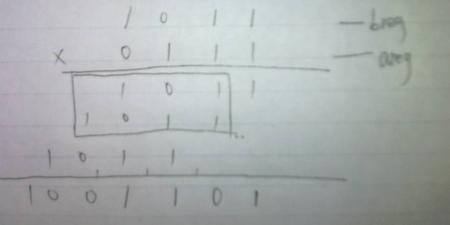

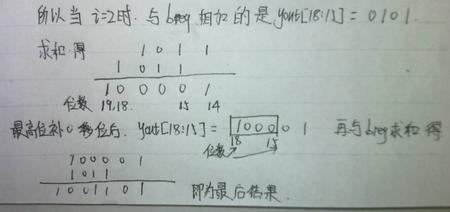

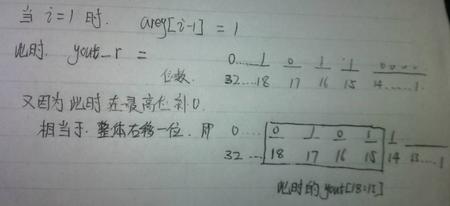

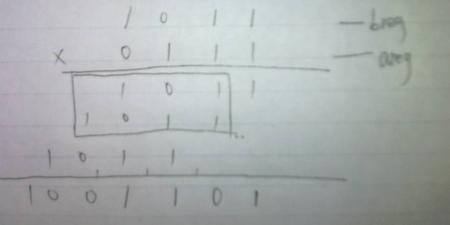

上次看了一下关于乘法器的Verilog代码,有几个地方一直很迷惑,相信很多初学者看这段代码一定跟我当初一样,看得一头雾水,在网上也有一些网友提问,说这段代码不好理解,今天小墨同学就和大家一起来看一下这段代码,我会亲自在草稿纸上演算,尽量把过程写的详细些,让更多的人了解乘法器的设计思路。

下面是一段16位乘法器的代码,大家可以先浏览一下,之后我再做详细解释

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

input clk; //芯片的时钟信号。

input rst_n; //低电平复位、清零信号。定义为0表示芯片复位;定义为1表示复位信号无效。

input start; //芯片使能信号。定义为0表示信号无效;定义为1表示芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。

input[15:0] ain; //输入a(被乘数),其数据位宽为16bit.

input[15:0] bin; //输入b(乘数),其数据位宽为16bit.

output[31:0] yout; //乘积输出,其数据位宽为32bit.

output done; //芯片输出标志信号。定义为1表示乘法运算完成.

reg[15:0] areg; //乘数a寄存器

reg[15:0] breg; //乘数b寄存器

reg[31:0] yout_r; //乘积寄存器

reg done_r;

reg[4:0] i; //移位次数寄存器

//------------------------------------------------

//数据位控制

always @(posedge clk or negedge rst_n)

if(!rst_n) i 5'd0 && i >1; //移位不累加

end

else if(i == 5'd16 && areg[15]) yout_r[31:16]

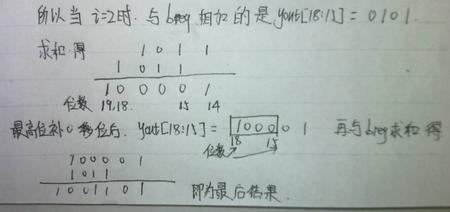

以上部分是最主要的计算部分,其他地方相对来说还比较简单,例如当乘数某一位为0时,不用累加,直接右移,当i计数到16时,此时就不用再移位了,可以直接用位数表示,直接累加即可。

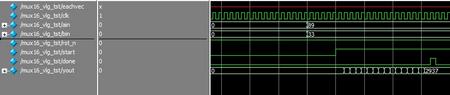

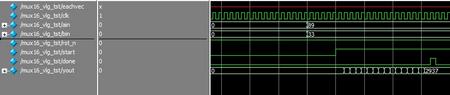

下面是仿真图

下面是一段16位乘法器的代码,大家可以先浏览一下,之后我再做详细解释

module mux16(

clk,rst_n,

start,ain,bin,yout,done

);

input clk; //芯片的时钟信号。

input rst_n; //低电平复位、清零信号。定义为0表示芯片复位;定义为1表示复位信号无效。

input start; //芯片使能信号。定义为0表示信号无效;定义为1表示芯片读入输入管脚得乘数和被乘数,并将乘积复位清零。

input[15:0] ain; //输入a(被乘数),其数据位宽为16bit.

input[15:0] bin; //输入b(乘数),其数据位宽为16bit.

output[31:0] yout; //乘积输出,其数据位宽为32bit.

output done; //芯片输出标志信号。定义为1表示乘法运算完成.

reg[15:0] areg; //乘数a寄存器

reg[15:0] breg; //乘数b寄存器

reg[31:0] yout_r; //乘积寄存器

reg done_r;

reg[4:0] i; //移位次数寄存器

//------------------------------------------------

//数据位控制

always @(posedge clk or negedge rst_n)

if(!rst_n) i 5'd0 && i >1; //移位不累加

end

else if(i == 5'd16 && areg[15]) yout_r[31:16]

以上部分是最主要的计算部分,其他地方相对来说还比较简单,例如当乘数某一位为0时,不用累加,直接右移,当i计数到16时,此时就不用再移位了,可以直接用位数表示,直接累加即可。

下面是仿真图

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)