零基础学FPGA(十三)先来说说VGA

时间:02-19

来源:互联网

点击:

这个实验其实已经做好久了,但是一直没有做笔记,今天就把这部分的内容补一下,有兴趣的朋友可以看一下,或许对你有什么帮助,对初学者来说还是一个不错的实验。

先来了解一下VGA吧

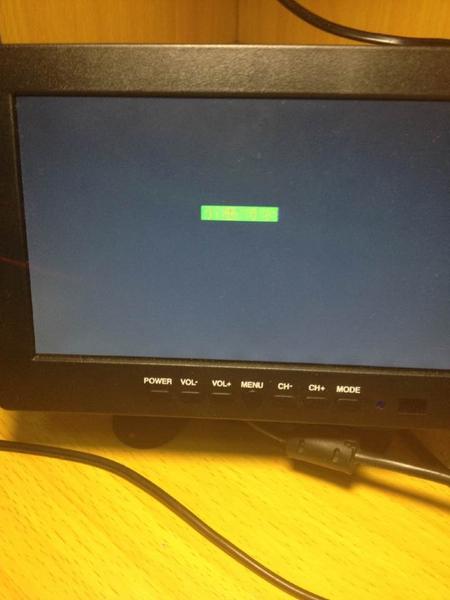

我们家里用的台式电脑就是一个VGA显示器,小墨同学为做这方面的实验还特意买了一块7寸的VGA液晶显示器

记得当初自己也是傻得不得了,把写好的代码,烧到板子里就直接连到笔记本电脑上的VGA接口上,结果什么反应也没有,还调了一下午的程序...结果还是没反应,到群里一问才知道,原来笔记本电脑上的VGA接口只能做输出而不能输入的这跟台式机还是不同的,后来才买的这块液晶显示器。

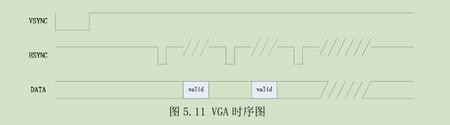

标准的VGA接口有15个接口,但是真正用到的只有5个接口,分别是三个色彩信号,R,G,B,场同步信号VSYNC,行同步信号HSYNC,时序部分要通过控制行同步信号和场同步信号,色彩部分要控制RGB,先来看时序部分。

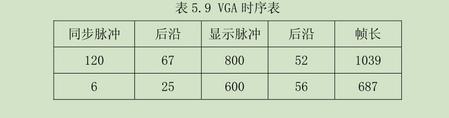

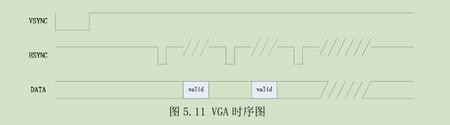

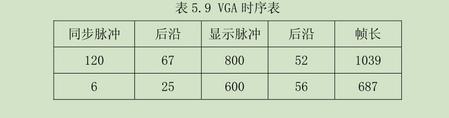

对于一个分辨率为800*600的显示器,简单的说像素的刷新是从左到右,从上到下一行一行的刷新的,每一行要刷新的点成为行同步信号的帧长,有多少行称为场同步信号的帧长,从上到下刷新完一遍称为一帧,我们电脑上说的屏幕刷新频率就是说屏幕一秒钟能够刷新多少帧,当达到一定的帧数,我们的肉眼也就分辨不出来了,这样我们就看到我们的电脑屏幕,我们在操作的时候是连续的了。下面是时序表:

先来解释一下这个表

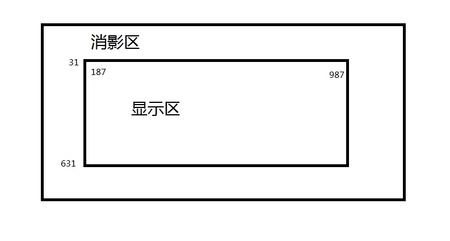

第一行表示行同步信号的时序表,前187个计数点表示的在消影区,即还没开始进入显示区,从188开始进入显示区,到987结束,后面的52个计数点又在消影区

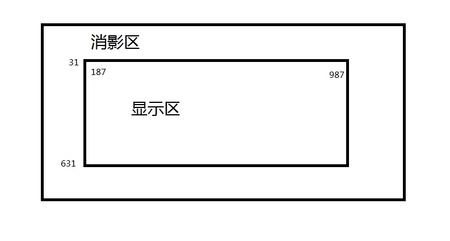

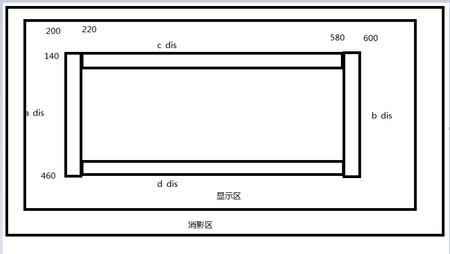

第二行表示场同步信号。同理。前31个计数点和后56个计数点表示在消影区,是不显示的,下面是我画的一个图帮大家理解

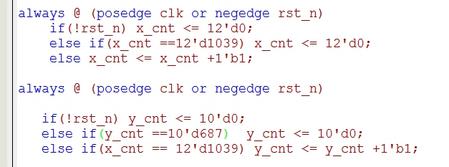

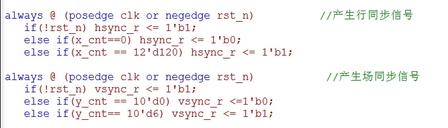

知道了这一点我们就可以开始写时序部分的程序了

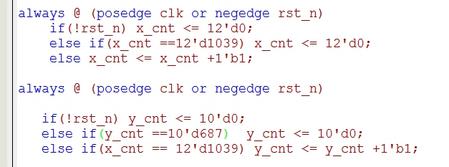

当行计数器计满一行1039个点时清零,场计数器加1,当场计数器计满687行时,一帧结束,场计数器清零

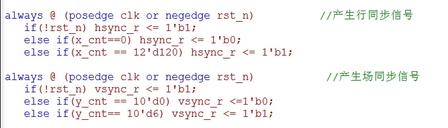

当计满一行时,行同步信号会拉低一个120个时钟周期的低脉冲,通俗的理解就是计满一行有一个低脉冲出现,这个脉冲的长度是120个时钟周期,同理,计满一个场之后会有6个场周期的低脉冲出现,这个低脉冲就不是时钟周期了,是相当于场计数器计6行的时间

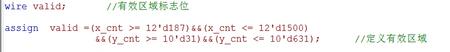

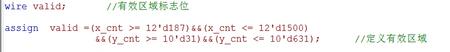

时序写好了之后就要确定显示区域,根据上面那个我画的图,即只有在行计数器计到187到987,场计数器计到31到631时才是有效区域

为了好确定坐标,我们可以将坐标转换一下,换成我们习惯的样子,避免消影区坐标的干扰

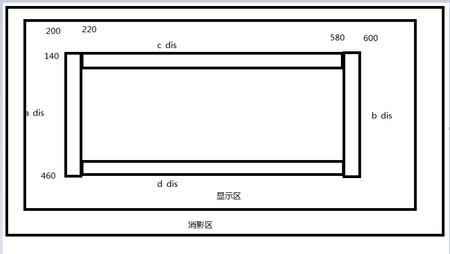

这样一切准备工作就做好了,剩下的就是我们自己设计想要显示的画面了,例如,我要在屏幕中间显示一个矩形框,在这个矩形里面显示一个小矩形

这个地方我刚开始看的时候没看懂,我再画一个图帮大家理解

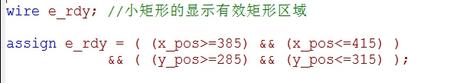

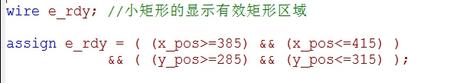

下面显示小矩形

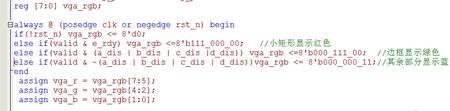

画完图形最后显示颜色

最后按照硬件原理图分配好管脚,下载就可以了

下面来说说显示字符

时序部分是一样的就不多说,直接说字符显示部分

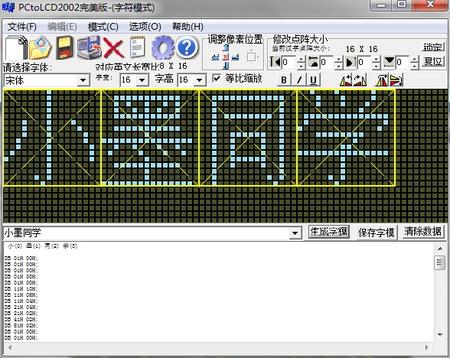

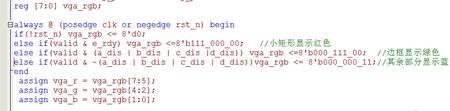

显示字符当然要用到取模软件,相信大家都用过

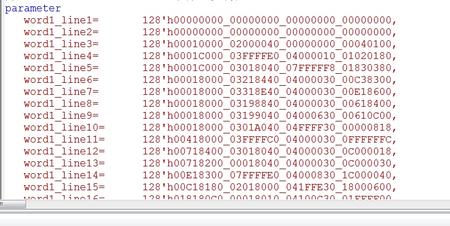

然后将字模进行拼接,因为我们刷新是从左向右,从上到下刷新的,所以要把每一个字模的同一行拼接在一起,这样每刷新一行,同时刷新三个字模的一行,从上到下刷新一边,三个字模也就刷新出来了

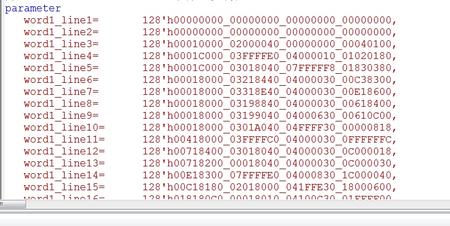

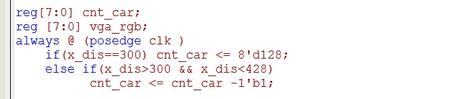

这里要定义一个减法计数器,当像素点从某个位置从左到右开始刷新时开始计数,知道计数到要显示的字模结束为止。这里我用到了32个像素点表示一个字模的一行,4个字模就需要128个像素点来表示一行,共有32列

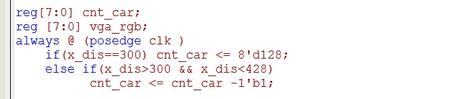

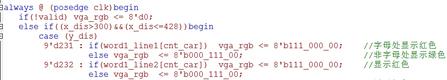

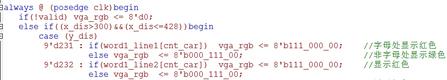

下面是当计数到需要显示的字模时,给字加上颜色,x_dis,y_dis用来确定在哪显示字符

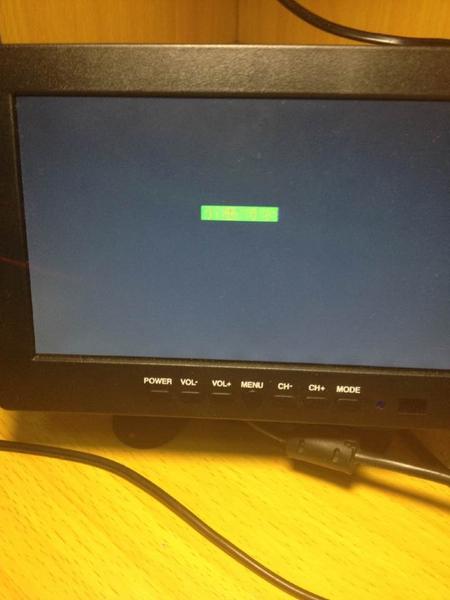

下面是演示结果

先来了解一下VGA吧

我们家里用的台式电脑就是一个VGA显示器,小墨同学为做这方面的实验还特意买了一块7寸的VGA液晶显示器

记得当初自己也是傻得不得了,把写好的代码,烧到板子里就直接连到笔记本电脑上的VGA接口上,结果什么反应也没有,还调了一下午的程序...结果还是没反应,到群里一问才知道,原来笔记本电脑上的VGA接口只能做输出而不能输入的这跟台式机还是不同的,后来才买的这块液晶显示器。

标准的VGA接口有15个接口,但是真正用到的只有5个接口,分别是三个色彩信号,R,G,B,场同步信号VSYNC,行同步信号HSYNC,时序部分要通过控制行同步信号和场同步信号,色彩部分要控制RGB,先来看时序部分。

对于一个分辨率为800*600的显示器,简单的说像素的刷新是从左到右,从上到下一行一行的刷新的,每一行要刷新的点成为行同步信号的帧长,有多少行称为场同步信号的帧长,从上到下刷新完一遍称为一帧,我们电脑上说的屏幕刷新频率就是说屏幕一秒钟能够刷新多少帧,当达到一定的帧数,我们的肉眼也就分辨不出来了,这样我们就看到我们的电脑屏幕,我们在操作的时候是连续的了。下面是时序表:

先来解释一下这个表

第一行表示行同步信号的时序表,前187个计数点表示的在消影区,即还没开始进入显示区,从188开始进入显示区,到987结束,后面的52个计数点又在消影区

第二行表示场同步信号。同理。前31个计数点和后56个计数点表示在消影区,是不显示的,下面是我画的一个图帮大家理解

知道了这一点我们就可以开始写时序部分的程序了

当行计数器计满一行1039个点时清零,场计数器加1,当场计数器计满687行时,一帧结束,场计数器清零

当计满一行时,行同步信号会拉低一个120个时钟周期的低脉冲,通俗的理解就是计满一行有一个低脉冲出现,这个脉冲的长度是120个时钟周期,同理,计满一个场之后会有6个场周期的低脉冲出现,这个低脉冲就不是时钟周期了,是相当于场计数器计6行的时间

时序写好了之后就要确定显示区域,根据上面那个我画的图,即只有在行计数器计到187到987,场计数器计到31到631时才是有效区域

为了好确定坐标,我们可以将坐标转换一下,换成我们习惯的样子,避免消影区坐标的干扰

这样一切准备工作就做好了,剩下的就是我们自己设计想要显示的画面了,例如,我要在屏幕中间显示一个矩形框,在这个矩形里面显示一个小矩形

这个地方我刚开始看的时候没看懂,我再画一个图帮大家理解

下面显示小矩形

画完图形最后显示颜色

最后按照硬件原理图分配好管脚,下载就可以了

下面来说说显示字符

时序部分是一样的就不多说,直接说字符显示部分

显示字符当然要用到取模软件,相信大家都用过

然后将字模进行拼接,因为我们刷新是从左向右,从上到下刷新的,所以要把每一个字模的同一行拼接在一起,这样每刷新一行,同时刷新三个字模的一行,从上到下刷新一边,三个字模也就刷新出来了

这里要定义一个减法计数器,当像素点从某个位置从左到右开始刷新时开始计数,知道计数到要显示的字模结束为止。这里我用到了32个像素点表示一个字模的一行,4个字模就需要128个像素点来表示一行,共有32列

下面是当计数到需要显示的字模时,给字加上颜色,x_dis,y_dis用来确定在哪显示字符

下面是演示结果

显示器 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- spartan6套件试用心得报告--001(05-10)