基于FPGA的跨时钟域信号处理——亚稳态

时间:02-19

来源:互联网

点击:

在特权的上篇博文《基于FPGA的跨时钟域信号处理——专用握手信号》中提出了使用专门的握手信号达到异步时钟域数据的可靠传输。列举了一个简单的由请求信号req、数据信号data、应答信号ack组成的简单握手机制。riple兄更是提出了req和ack这两个直接的跨时钟域信号在被另一个时钟域的寄存器同步时的亚稳态问题。这个问题估计是整个异步通信中最值得探讨和关注的。

很幸运,特权同学找到了很官方的说法——《Application Note42:Metastability in Altera Devices》,一口气读完全文,有一个单词送给这篇文章很合适——“nice”。特权同学过去的所有疑惑都在文章中找到了答案,尽管altera在文章的最后只是竭尽全力的在吹捧自己的好。

如果你E文还不错(该不会比我这个4次都没过掉4级考试的家伙差吧,~_~),那么去享受原文吧。或者你可以考虑看看特权同学的翻译水平,哈哈……

什么是亚稳态?

所有数字器件(例如FPGA)的信号传输都会有一定的时序要求,从而保证每个寄存器将捕获的输入信号正确输出。为了确保可靠的操作,输入寄存器的信号必须在时钟沿的某段时间(寄存器的建立时间Tsu)之前保持稳定,并且持续到时钟沿之后的某段时间(寄存器的保持时间Th)之后才能改变。而该寄存器的输入反映到输出则需要经过一定的延时(时钟到输出的时间Tco)。如果数据信号的变化违反了Tsu后者Th的要求,那么寄存器的输出就会处于亚稳态。此时,寄存器的输出会在高电平1和低电平0之间盘旋一段时间,这也意味着寄存器的输出达到一个稳定的高或者低电平的状态所需要的时间会大于Tco。

在同步系统中,输入信号总是能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号的传输上。由于数据信号可能在任何时间到达异步时钟域的目的寄存器,所以设计者无法保证满足Tsu和Th的要求。然而,并非所有违反寄存器的Tsu或Th要求的信号会导致输出亚稳态。某个寄存器进入了亚稳态后重新回到稳定状态的时间取决于器件的制造工艺及工作环境。在大多数情况下,寄存器将会快速的返回稳定状态。

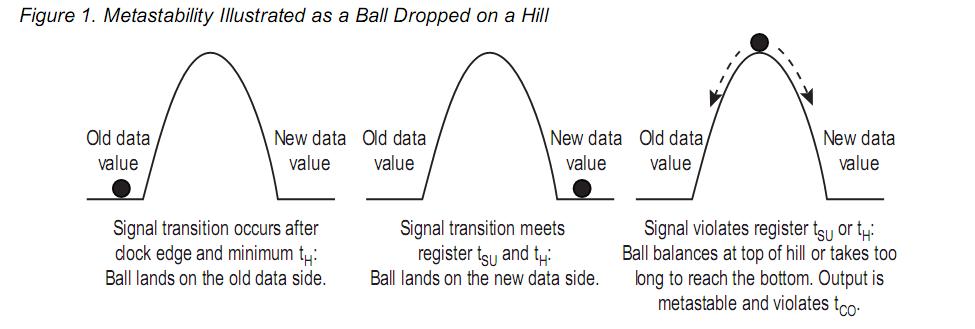

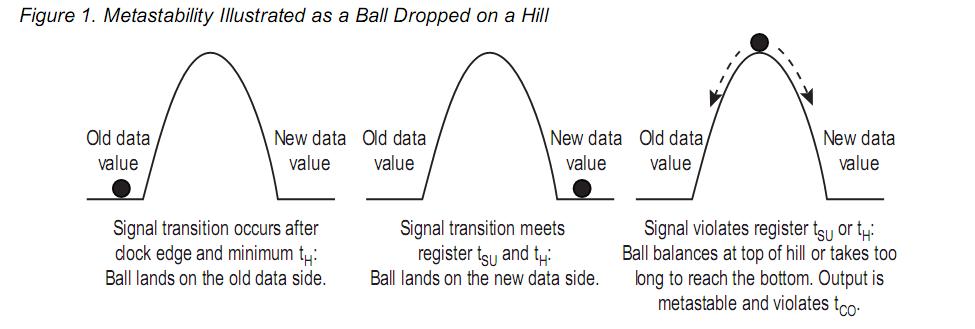

寄存器在时钟沿采样数据信号好比一个球从小山的一侧抛到另一侧。如图1所示,小山的两侧代表数据的稳定状态——旧的数据值或者新的数据值;山顶代表亚稳态。如果球被抛到山顶上,它可能会停在山顶上,但实际上它只要稍微有些动静就会滚落到山底。在一定时间内,球滚的越远,它达到稳定状态的时间也就越短。

如果数据信号的变化发生在时钟沿的某段时间之后(Th),就好像球跌落到了小山的“old data value”一侧,输出信号仍然保持时钟变化前的值不变。如果数据信号的变化发生在时钟沿的某段时间(Tsu)之前,并且持续到时钟沿之后的某段时间(Th)都不再变化,那就好像球跌落到了小山的“new data value”一侧,输出数据达到稳定状态的时间为Tco。然而,当一个寄存器的输入数据违反了Tsu或者Th,就像球被抛到了山顶。如果球在山顶停留的越久,那么它到达山底的时间也就越长,这就相应的延长了从时钟变化到输出数据达到稳定状态的时间(Tco)。

图1

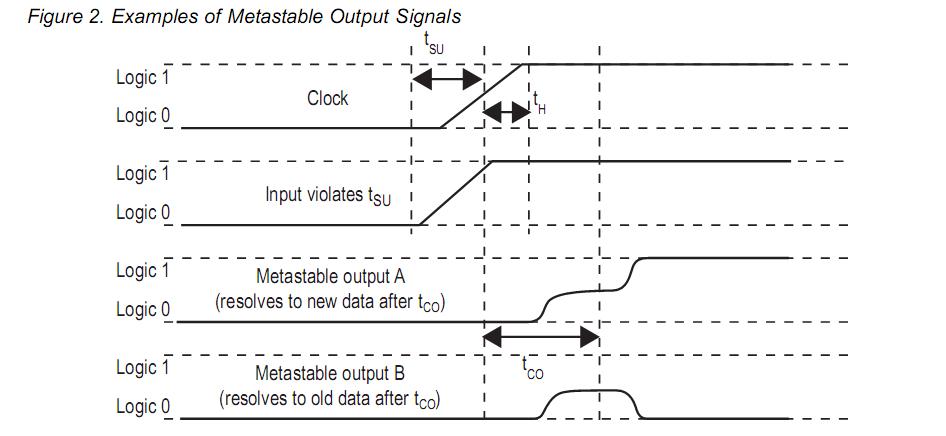

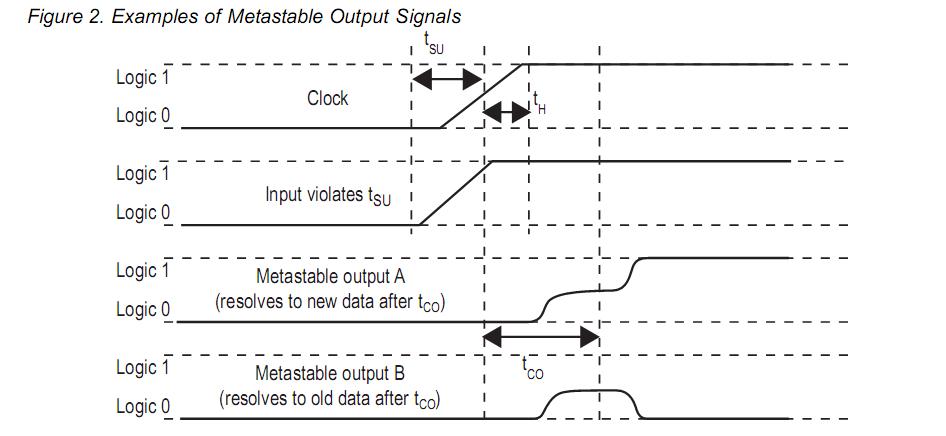

图2很好的阐释了亚稳态信号。在时钟变化的同时,寄存器的输入数据信号也处于从低电平到高电平的变化状态,这就违反了寄存器的Tsu要求。图中的输出信号从低电平变化到亚稳态,即盘旋于高低电平之间的一个状态。信号输出A最终达到输入信号的新状态值1,信号输出B却返回了输入信号的旧状态值0。在这两种情况下,信号输出变化稳定在固定的1或者0状态的时间远超过了寄存器的固有Tco。

图2

如果输出信号在下一个寄存器捕获数据前(下一个时钟锁存沿的Tsu时间前)处于一个稳定的有效状态,那么亚稳态信号不会对该系统照成影响。但是如果亚稳态信号在下一个寄存器捕获数据时仍然盘旋于高或者低电平之间,那将会对系统的后续电路产生影响。继续讨论球和小山的比喻,当球到达山底的时间(处于稳定的逻辑值0或1)超过了扣除寄存器Tco以外的余量时间,那么问题就随着而来。

同步寄存器

当信号变化处于一个不相关的电路或者以不时钟域,它在被使用前就需要先被同步到新的时钟域中。新的时钟域中的第一个寄存器将扮演同步寄存器的角色。

为了尽可能减少异步信号传输中由于亚稳态引发的问题,设计者通常在目的时钟域中使用一串连续的寄存器(同步寄存器链或者同步装置)将信号同步到新的时钟域中。这些寄存器有额外的时间用于信号在被使用前从亚稳态达到稳定值。同步寄存器到寄存器路径的时序余量,也就是亚稳态信号达到稳定的最大时间,也被认为是亚稳态持续时间。

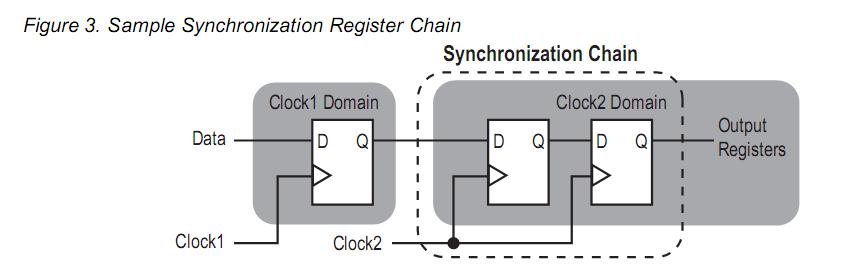

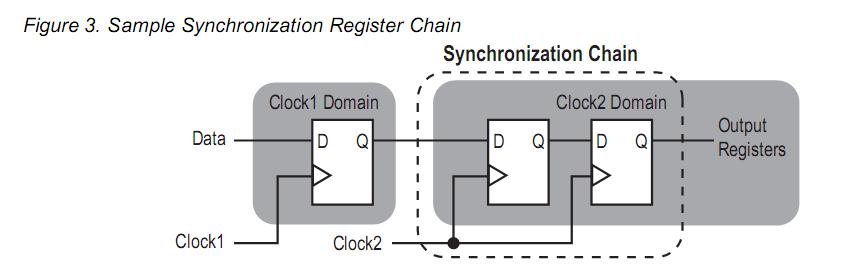

同步寄存器链,或者同步装置,被定义为一串达到以下要求的连续寄存器:

■ 链中的寄存器都由相同的时钟或者相位相关的时钟触发;

■ 链中的第一个寄存器由不相关时钟域或者是异步的时钟来触发;

■ 每个寄存器的扇出值都为1,链中的最后一个寄存器可以例外。

同步寄存器链的长度就是达到以上要求的同步时钟域的寄存器数量,图3是一个两级的同步寄存器链,

图3

传输在不相关时钟域的信号,都有可能在相对于捕获寄存器时钟沿的任何时间点变化。因此,设计者无法预测信号变化的顺序或者说信号两次变化间经过了几个锁存时钟周期。例如,一条异步总线的各个数据信号可能在不同的时钟沿变化,结果接收到的数据值可能是错误的。

设计者必须考虑到电路的这些情况,而使用双时钟FIFO(DCFIFO)传输信号或者使用握手信号进行控制。FIFO使用同步装置处理来自不同时钟域的控制信号,数据的读写使用两套独立的总线。此外,如果异步信号作为两个时钟域的握手逻辑,这些控制信号就需要用于指示何时数据信号可以被接收时钟域锁存。如此一来,就可以利用同步寄存器确保亚稳态不会影响控制信号的传输,从而保证数据在使用前有充足的时间等待亚稳态达到稳定。

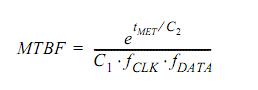

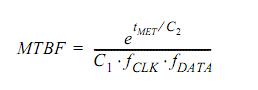

文章其实还没有结束,只不过altera在后面很官方的提出了所谓的MTBF(mean time between failures)的概念,即所谓的平均无故障时间的概念。列了个公式,分析了各个参数,当然也不忘提他们的器件参数对于这个MTBF做了多大的贡献。然后也提出了它们是如何进行该公式参数的推导。

我们还是回到主题,在明确了这些基本的概念和基本的方法后,就要学以致用。在上篇博文没有解决的一个关键问题在于如何最有效的进行握手信号req、ack的采样。这个问题我们可以先以altera提出的MTBF推导公式的各个参数入手分析。

在这个公式中,Tmet就是指寄存器从时钟上升沿触发后的时序余量时间,Fclk是接收时钟域的时钟频率,Fdata是数据的变化频率,而C1、C2则是与器件有关的参数,对于用户是一个固定值。由此看来,设计者只能通过改变Tmet、Fclk、Fdata来提高MTBF值。MTBF值越大,说明出现亚稳态的几率越小。要增大MTBF值,可以延长Tmet、也可以降低Fclk和Fdata这两个频率。

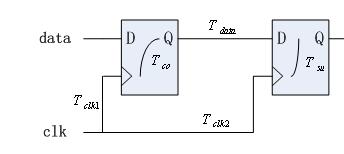

首先我们看看如何延长Tmet时间。

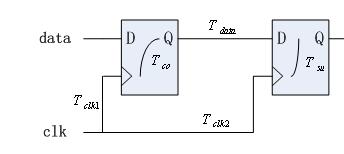

Tmet时间 = 采样时钟周期时间 – 输出信号正常的Tco时间 - 数据到达下一级寄存器的输入端口的其它延时时间Tdata - 下一级寄存器Tsu时间。

图4

从严格意义上来说,Tmet时间还应该加上时钟网络延时时间(Tclk2-Tclk1)。总之,这个Tmet时间是指正常没有亚稳态情况下,寄存器输出信号从源寄存器到目的寄存器的建立时间余量。由于决定Tmet取值的参数中Tco和Tsu都是由FPGA器件本身的工艺以及工作环境决定的,设置时钟网络延时参数也很大程度上由器件决定,所以,如果在时钟频率Fclk和数据变化率Fdata固定的情况下,要增大Tmet值,那么设计者要做的只能是减小Tdata值。而这个Tdata是指两个寄存器间的逻辑延时以及走线延时之和,要最大程度的减小它,估计也只能是不在连个寄存器间添加任何逻辑而已,正如我们的实例中也只有简单的input=output。

再看Fclk,它是接收域的采样时钟,就是异步信号需要被同步到的那个时钟域,它的频率是越小越好。当然了,事物都其两面性,这个频率小到影响系统正常工作可就不行了。设计者需要从各个方面考虑来决定这个频率,不会仅仅为了降低亚稳态发生的概率而无限制的降低系统的时钟频率。如此分析,发现这个Fclk基本也是一个比较固定的值,不是可以随便说降就降的。降低Fclk其实也就是在增大Tmet时间,因为它是Tmet公式计算中的被减数,哈哈,好像是一环扣一环。另外,在不降低采样频率Fclk的情况下,通过使用使能信号的方式得到一个二分频时钟去采样信号也可以达到降频的目的,只不过这样会多耗费几个时钟周期用于同步,但是有时也能够明显改善性能。

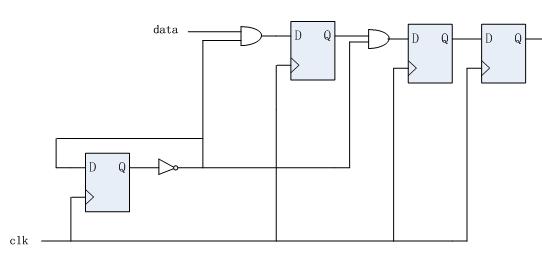

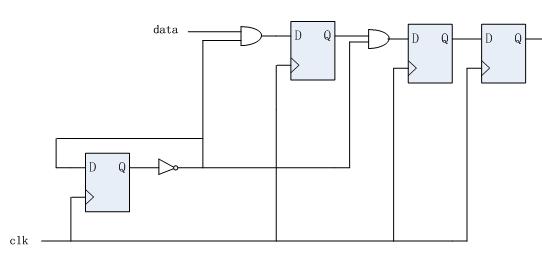

特权同学的二分频采样思路如图5所示,前两级采样电路都做了2分频,然后第三级使用原来时钟进行采样。它的好处在于给第一级和第二级同步寄存器更多的Tmet时间,将亚稳态抑制在第二级寄存器输入之前,从而保证第三级寄存器的可靠采样。虽然它在一、二级寄存器的输入端增加了一些逻辑,可能会增大Tdata,但是相比于这个采样时钟的一半将额,它的变化是可以忽略不计的。

图5

另一种办法是在不降低每级寄存器的采样频率的情况下采用更多的同步寄存器,尽量去使用后级的寄存器,这也是一个笨办法。Altera的笔记里打了一个比喻,如果一个设计你使用了9级的同步寄存器,那么MTBF是100年,而当你使用了10级的同步寄存器,那么MTBF是1000年。这个办法其实有点类似冗余,这是所有人都知道的可以提高可靠性的原始办法。这种思路的弊端和前面提到的方法一样,需要付出多个时钟周期为代价。

最后看这个Fdata,这个是发送时钟域的数据变化率,似乎也是由系统决定的,设计者也无法做太多改变。

其实对于一般的应用,如果系统的时钟频率不太高,器件的特性还算可以(只是一些泛泛的说法,具体问题要具体分析),特权同学觉得上篇博文提出的握手信号同步方法就足以应付亚稳态问题。如果到高频范畴来讨论亚稳态,那将会是一项更有挑战性的任务,只可惜特权同学目前接触的最高频也只不过100MHz而已。特权同学自觉才疏学浅,班门弄斧了。

无独有偶,特权同学这篇博文即将收官之际,无意中看到船长的博客中《理解FPGAs中的亚稳态》一文也涉及到了altera的这篇笔记,也做了一下翻译,似乎比特权同学翻译的好。不过在此做个声明,特权同学的博文一贯坚持原创,即便参考其它资料,也大都有所提及,并且有自己的评论和思考,这应该是每位电子工程师应该有的严谨和认真的态度。

很幸运,特权同学找到了很官方的说法——《Application Note42:Metastability in Altera Devices》,一口气读完全文,有一个单词送给这篇文章很合适——“nice”。特权同学过去的所有疑惑都在文章中找到了答案,尽管altera在文章的最后只是竭尽全力的在吹捧自己的好。

如果你E文还不错(该不会比我这个4次都没过掉4级考试的家伙差吧,~_~),那么去享受原文吧。或者你可以考虑看看特权同学的翻译水平,哈哈……

什么是亚稳态?

所有数字器件(例如FPGA)的信号传输都会有一定的时序要求,从而保证每个寄存器将捕获的输入信号正确输出。为了确保可靠的操作,输入寄存器的信号必须在时钟沿的某段时间(寄存器的建立时间Tsu)之前保持稳定,并且持续到时钟沿之后的某段时间(寄存器的保持时间Th)之后才能改变。而该寄存器的输入反映到输出则需要经过一定的延时(时钟到输出的时间Tco)。如果数据信号的变化违反了Tsu后者Th的要求,那么寄存器的输出就会处于亚稳态。此时,寄存器的输出会在高电平1和低电平0之间盘旋一段时间,这也意味着寄存器的输出达到一个稳定的高或者低电平的状态所需要的时间会大于Tco。

在同步系统中,输入信号总是能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号的传输上。由于数据信号可能在任何时间到达异步时钟域的目的寄存器,所以设计者无法保证满足Tsu和Th的要求。然而,并非所有违反寄存器的Tsu或Th要求的信号会导致输出亚稳态。某个寄存器进入了亚稳态后重新回到稳定状态的时间取决于器件的制造工艺及工作环境。在大多数情况下,寄存器将会快速的返回稳定状态。

寄存器在时钟沿采样数据信号好比一个球从小山的一侧抛到另一侧。如图1所示,小山的两侧代表数据的稳定状态——旧的数据值或者新的数据值;山顶代表亚稳态。如果球被抛到山顶上,它可能会停在山顶上,但实际上它只要稍微有些动静就会滚落到山底。在一定时间内,球滚的越远,它达到稳定状态的时间也就越短。

如果数据信号的变化发生在时钟沿的某段时间之后(Th),就好像球跌落到了小山的“old data value”一侧,输出信号仍然保持时钟变化前的值不变。如果数据信号的变化发生在时钟沿的某段时间(Tsu)之前,并且持续到时钟沿之后的某段时间(Th)都不再变化,那就好像球跌落到了小山的“new data value”一侧,输出数据达到稳定状态的时间为Tco。然而,当一个寄存器的输入数据违反了Tsu或者Th,就像球被抛到了山顶。如果球在山顶停留的越久,那么它到达山底的时间也就越长,这就相应的延长了从时钟变化到输出数据达到稳定状态的时间(Tco)。

图1

图2很好的阐释了亚稳态信号。在时钟变化的同时,寄存器的输入数据信号也处于从低电平到高电平的变化状态,这就违反了寄存器的Tsu要求。图中的输出信号从低电平变化到亚稳态,即盘旋于高低电平之间的一个状态。信号输出A最终达到输入信号的新状态值1,信号输出B却返回了输入信号的旧状态值0。在这两种情况下,信号输出变化稳定在固定的1或者0状态的时间远超过了寄存器的固有Tco。

图2

如果输出信号在下一个寄存器捕获数据前(下一个时钟锁存沿的Tsu时间前)处于一个稳定的有效状态,那么亚稳态信号不会对该系统照成影响。但是如果亚稳态信号在下一个寄存器捕获数据时仍然盘旋于高或者低电平之间,那将会对系统的后续电路产生影响。继续讨论球和小山的比喻,当球到达山底的时间(处于稳定的逻辑值0或1)超过了扣除寄存器Tco以外的余量时间,那么问题就随着而来。

同步寄存器

当信号变化处于一个不相关的电路或者以不时钟域,它在被使用前就需要先被同步到新的时钟域中。新的时钟域中的第一个寄存器将扮演同步寄存器的角色。

为了尽可能减少异步信号传输中由于亚稳态引发的问题,设计者通常在目的时钟域中使用一串连续的寄存器(同步寄存器链或者同步装置)将信号同步到新的时钟域中。这些寄存器有额外的时间用于信号在被使用前从亚稳态达到稳定值。同步寄存器到寄存器路径的时序余量,也就是亚稳态信号达到稳定的最大时间,也被认为是亚稳态持续时间。

同步寄存器链,或者同步装置,被定义为一串达到以下要求的连续寄存器:

■ 链中的寄存器都由相同的时钟或者相位相关的时钟触发;

■ 链中的第一个寄存器由不相关时钟域或者是异步的时钟来触发;

■ 每个寄存器的扇出值都为1,链中的最后一个寄存器可以例外。

同步寄存器链的长度就是达到以上要求的同步时钟域的寄存器数量,图3是一个两级的同步寄存器链,

图3

传输在不相关时钟域的信号,都有可能在相对于捕获寄存器时钟沿的任何时间点变化。因此,设计者无法预测信号变化的顺序或者说信号两次变化间经过了几个锁存时钟周期。例如,一条异步总线的各个数据信号可能在不同的时钟沿变化,结果接收到的数据值可能是错误的。

设计者必须考虑到电路的这些情况,而使用双时钟FIFO(DCFIFO)传输信号或者使用握手信号进行控制。FIFO使用同步装置处理来自不同时钟域的控制信号,数据的读写使用两套独立的总线。此外,如果异步信号作为两个时钟域的握手逻辑,这些控制信号就需要用于指示何时数据信号可以被接收时钟域锁存。如此一来,就可以利用同步寄存器确保亚稳态不会影响控制信号的传输,从而保证数据在使用前有充足的时间等待亚稳态达到稳定。

文章其实还没有结束,只不过altera在后面很官方的提出了所谓的MTBF(mean time between failures)的概念,即所谓的平均无故障时间的概念。列了个公式,分析了各个参数,当然也不忘提他们的器件参数对于这个MTBF做了多大的贡献。然后也提出了它们是如何进行该公式参数的推导。

我们还是回到主题,在明确了这些基本的概念和基本的方法后,就要学以致用。在上篇博文没有解决的一个关键问题在于如何最有效的进行握手信号req、ack的采样。这个问题我们可以先以altera提出的MTBF推导公式的各个参数入手分析。

在这个公式中,Tmet就是指寄存器从时钟上升沿触发后的时序余量时间,Fclk是接收时钟域的时钟频率,Fdata是数据的变化频率,而C1、C2则是与器件有关的参数,对于用户是一个固定值。由此看来,设计者只能通过改变Tmet、Fclk、Fdata来提高MTBF值。MTBF值越大,说明出现亚稳态的几率越小。要增大MTBF值,可以延长Tmet、也可以降低Fclk和Fdata这两个频率。

首先我们看看如何延长Tmet时间。

Tmet时间 = 采样时钟周期时间 – 输出信号正常的Tco时间 - 数据到达下一级寄存器的输入端口的其它延时时间Tdata - 下一级寄存器Tsu时间。

图4

从严格意义上来说,Tmet时间还应该加上时钟网络延时时间(Tclk2-Tclk1)。总之,这个Tmet时间是指正常没有亚稳态情况下,寄存器输出信号从源寄存器到目的寄存器的建立时间余量。由于决定Tmet取值的参数中Tco和Tsu都是由FPGA器件本身的工艺以及工作环境决定的,设置时钟网络延时参数也很大程度上由器件决定,所以,如果在时钟频率Fclk和数据变化率Fdata固定的情况下,要增大Tmet值,那么设计者要做的只能是减小Tdata值。而这个Tdata是指两个寄存器间的逻辑延时以及走线延时之和,要最大程度的减小它,估计也只能是不在连个寄存器间添加任何逻辑而已,正如我们的实例中也只有简单的input=output。

再看Fclk,它是接收域的采样时钟,就是异步信号需要被同步到的那个时钟域,它的频率是越小越好。当然了,事物都其两面性,这个频率小到影响系统正常工作可就不行了。设计者需要从各个方面考虑来决定这个频率,不会仅仅为了降低亚稳态发生的概率而无限制的降低系统的时钟频率。如此分析,发现这个Fclk基本也是一个比较固定的值,不是可以随便说降就降的。降低Fclk其实也就是在增大Tmet时间,因为它是Tmet公式计算中的被减数,哈哈,好像是一环扣一环。另外,在不降低采样频率Fclk的情况下,通过使用使能信号的方式得到一个二分频时钟去采样信号也可以达到降频的目的,只不过这样会多耗费几个时钟周期用于同步,但是有时也能够明显改善性能。

特权同学的二分频采样思路如图5所示,前两级采样电路都做了2分频,然后第三级使用原来时钟进行采样。它的好处在于给第一级和第二级同步寄存器更多的Tmet时间,将亚稳态抑制在第二级寄存器输入之前,从而保证第三级寄存器的可靠采样。虽然它在一、二级寄存器的输入端增加了一些逻辑,可能会增大Tdata,但是相比于这个采样时钟的一半将额,它的变化是可以忽略不计的。

图5

另一种办法是在不降低每级寄存器的采样频率的情况下采用更多的同步寄存器,尽量去使用后级的寄存器,这也是一个笨办法。Altera的笔记里打了一个比喻,如果一个设计你使用了9级的同步寄存器,那么MTBF是100年,而当你使用了10级的同步寄存器,那么MTBF是1000年。这个办法其实有点类似冗余,这是所有人都知道的可以提高可靠性的原始办法。这种思路的弊端和前面提到的方法一样,需要付出多个时钟周期为代价。

最后看这个Fdata,这个是发送时钟域的数据变化率,似乎也是由系统决定的,设计者也无法做太多改变。

其实对于一般的应用,如果系统的时钟频率不太高,器件的特性还算可以(只是一些泛泛的说法,具体问题要具体分析),特权同学觉得上篇博文提出的握手信号同步方法就足以应付亚稳态问题。如果到高频范畴来讨论亚稳态,那将会是一项更有挑战性的任务,只可惜特权同学目前接触的最高频也只不过100MHz而已。特权同学自觉才疏学浅,班门弄斧了。

无独有偶,特权同学这篇博文即将收官之际,无意中看到船长的博客中《理解FPGAs中的亚稳态》一文也涉及到了altera的这篇笔记,也做了一下翻译,似乎比特权同学翻译的好。不过在此做个声明,特权同学的博文一贯坚持原创,即便参考其它资料,也大都有所提及,并且有自己的评论和思考,这应该是每位电子工程师应该有的严谨和认真的态度。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)