CPLD对FPGA从并快速加载的解决方案

时间:11-10

来源:互联网

点击:

现场可编程门阵列(FPGA)作为专用集成电路(ASIC)领域的一种半定制电路,可以根据设计的需要灵活实现各种接口或者总线的输出,在设备端的通信产品中已得到越来越广泛的使用。FPGA是基于静态随机存储器(SRAM)结构的,断电后程序丢失后的每次上电都需要重新加载程序。且随着FPGA规模的升级,加载程序的容量也越来越大,如Xilinx公司的Spartan - 6系列中的6SLX150T,其加载容量最大可以达到4.125 MB.

1 FPGA常用配置方式

FPGA的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit文件并加载到FPGA中,配置方式有JTAG、从并、从串、主从4种,不同厂家叫法不同,但实现方式基本都是一样的。

(1)边界扫描JTAG方式。单板调试阶段常用JTAG模式,该方式需要控制器,FPGA等芯片JTAG接口构成菊花链,且在该模式下,控制器其他功能不能使用。

(2)从串方式。从串加载方式占用资源少,主要是和FPGA相连的I/O接口较少,但是一个配置时钟只能传输一个bit数据,速度相对较低。

(3)主从方式。该方式最主要的缺点是配套使用的FLASH存储器必须是FPGA厂家指定的型号,且这个FLASH容量不大,不能和控制器的FLASH共用,使用这种方式,单板上就会有两个FLASH,增加产品成本,因此该方案使用较少。

(4)从并方式。即文章中探讨的FPGA加载方案。

2从并加载方式的实现

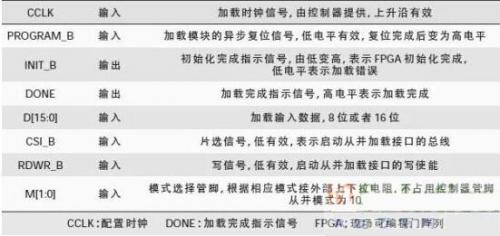

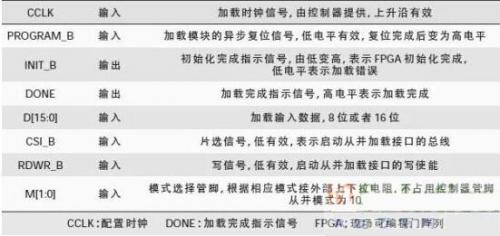

以Xilinx公司Spartan - 6系列FPGA为例,与从并加载相关的管脚如表1所示。

表1从并加载管脚名称

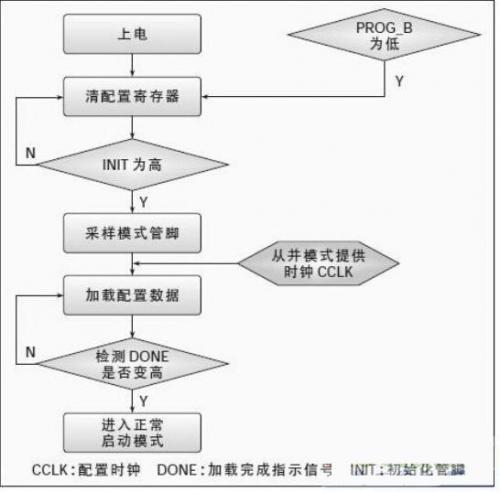

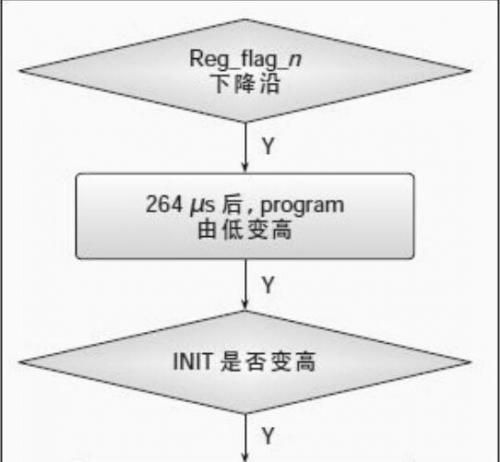

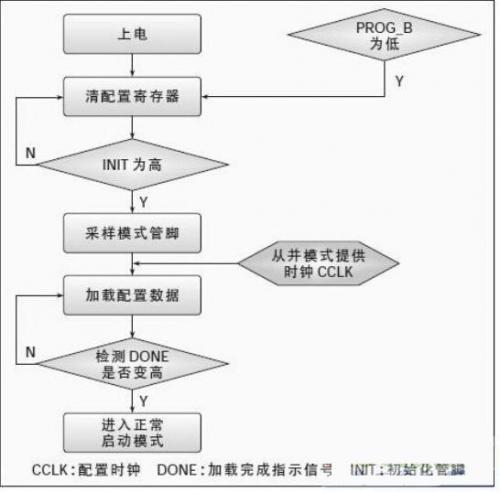

由表1可以看出,从并加载接口占用的管脚资源是比较多的,即使加载数据总线使用8位,也要14个管脚,CPU一般没有这么多通用输入/输出(GPIO)口,因此从并加载一般和CPLD配套使用。其加载流程如图1所示。

图1 SPARTAN-6从并加载流程

3基于CPLD的FPGA加载方案

3.1方案介绍

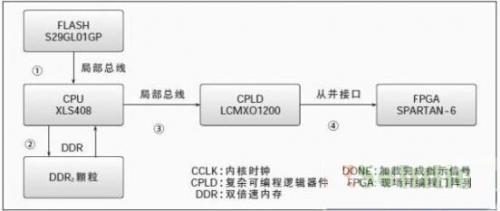

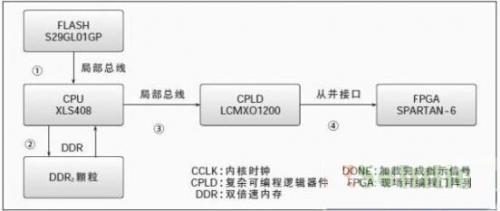

在设备端通信产品中,基于CPLD的FPGA从并加载框如图2所示,配置数据存储在FLASH中,且在加载数据之前,CPU通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH中搬移到DDR颗粒;真正需要加载时,再通过DDR2接口将配置数据搬移到CPU的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图2基于CPLD的FPGA从并加载框

之后CPU通过和CPLD的接口③——8位的局部总线接口,将配置数据逐字节的写入CPLD的寄存器中。以MIPS系列CPU XLS408为例,XLS408工作时钟频率为66.7 MHz,写总线周期最快需要10个工作时钟周期,即6.67 MHz,这一步受局部总线速度限制。

数据写入到CPLD后,再通过接口④——CPLD与FPGA之间的从并接口,将数据加载到FPGA,从并接口是同步总线,加载时间受限于总线时钟CCLK频率。

本方案的优点为:①、②两条路径可以在加载之前处理,且运行速度快,不占用加载时间。加载时间只受③、④的限制,而③受限于写总线周期间隔,④受限于从并接口的时钟。

3.2程序实现

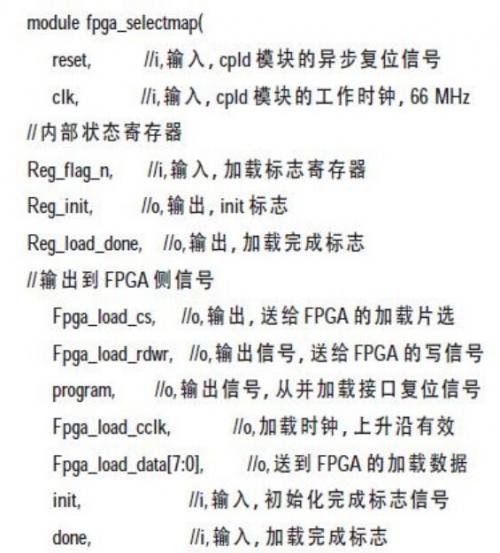

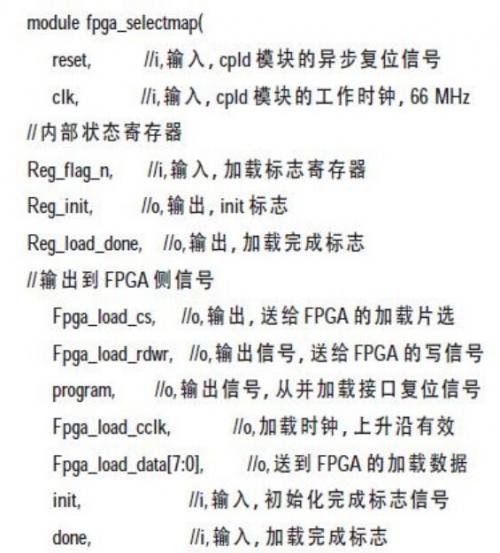

CPLD从并程序采用verilog语言实现,该加载模块接口定义如下:

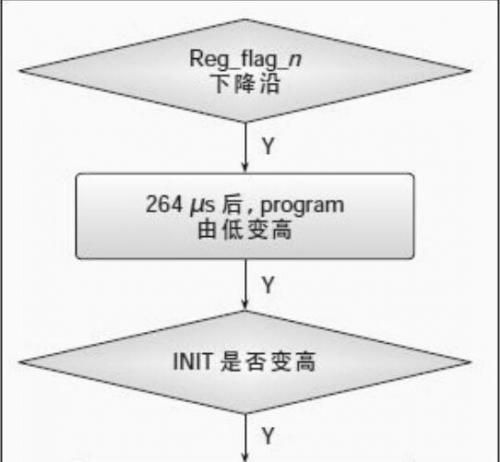

程序实现流如图3所示。

图3基于CPLD从并加载FPGA的程序流程

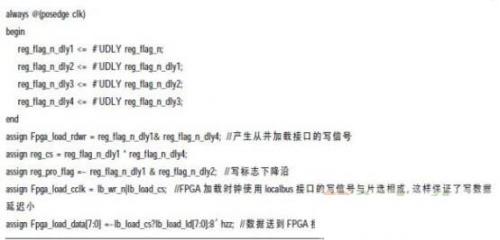

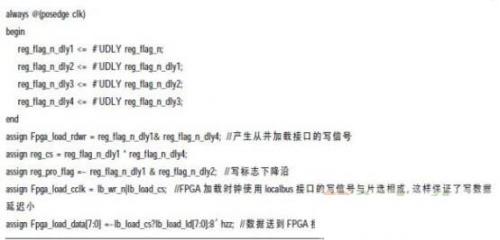

FPGA加载片选和写信号产生部分代码如下:

4仿真及加载结果分析

基于modelsim 6.5SE仿真波形可以看出CPU每加载1字节数据需要向CPLD写1次加载数据,这共需花费一个局部总线周期,局部总线频率最快为6.67 MHz.因此CPU加载4.125 MB数据到CPLD共需时间为:

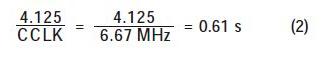

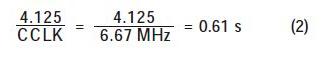

CPLD需要1个CCLK周期写1字节数据到FPGA,CCLK则是利用CPU局部总线的写信号产生,可以实现CCLK和数据的同步,因此CCLK时钟速率为6.67 MHz,因此加载4.125 MB数据到FPGA,共需时间为:

FPGA上电需要1 ms,因此当FPGA使用SPARTAN-6系列最高端的6SLX150T时,采用基于CPLD的从并加载方式,共需要的加载时间为1.221 s,满足通信产品FPGA加载时间小于2 s的要求。而如果采用从串等加载方式,使用ARM7处理器作为控制器,对于CycloneII系列中的EP2C35,配置文件大小1.16 MB,加载时间需要1.30 min;采用基于CPLD的从串加载方式,加载同样4.125 MB的FPGA数据,CPLD加载时钟33MHz,则加载时间需要3.8 s,FPGA加载时间过长,则会影响系统的启动时间。

表2是常用加载方式加载6SLX150T型号FPGA芯片数据所需时间比较。

表2 FPGA加载时间对比

从上述分析可以得出结论,如果提高CPU的局部总线写速度,加载FPGA的时间就会更快。

5结束语

使用基于CPLD的FPGA从并加载方案,相对于其它几种加载方式,虽然加载管脚增多,但加载时间大大缩短,并且如果提高CPU局部总线的写速度,加载速度有进一步提高空间,满足通信系统快速启动的要求,具有很高的实用价值。

1 FPGA常用配置方式

FPGA的配置数据通常存放在系统中的存储器件中,上电后控制器读取存储器中的bit文件并加载到FPGA中,配置方式有JTAG、从并、从串、主从4种,不同厂家叫法不同,但实现方式基本都是一样的。

(1)边界扫描JTAG方式。单板调试阶段常用JTAG模式,该方式需要控制器,FPGA等芯片JTAG接口构成菊花链,且在该模式下,控制器其他功能不能使用。

(2)从串方式。从串加载方式占用资源少,主要是和FPGA相连的I/O接口较少,但是一个配置时钟只能传输一个bit数据,速度相对较低。

(3)主从方式。该方式最主要的缺点是配套使用的FLASH存储器必须是FPGA厂家指定的型号,且这个FLASH容量不大,不能和控制器的FLASH共用,使用这种方式,单板上就会有两个FLASH,增加产品成本,因此该方案使用较少。

(4)从并方式。即文章中探讨的FPGA加载方案。

2从并加载方式的实现

以Xilinx公司Spartan - 6系列FPGA为例,与从并加载相关的管脚如表1所示。

表1从并加载管脚名称

由表1可以看出,从并加载接口占用的管脚资源是比较多的,即使加载数据总线使用8位,也要14个管脚,CPU一般没有这么多通用输入/输出(GPIO)口,因此从并加载一般和CPLD配套使用。其加载流程如图1所示。

图1 SPARTAN-6从并加载流程

3基于CPLD的FPGA加载方案

3.1方案介绍

在设备端通信产品中,基于CPLD的FPGA从并加载框如图2所示,配置数据存储在FLASH中,且在加载数据之前,CPU通过局部总线和双倍速内存(DDR)接口,将配置数据从FLASH中搬移到DDR颗粒;真正需要加载时,再通过DDR2接口将配置数据搬移到CPU的缓存中,DDR2接口速度很快,其时钟频率可以达到266 MHz,因此①、②两步加载时间可以忽略不计。

图2基于CPLD的FPGA从并加载框

之后CPU通过和CPLD的接口③——8位的局部总线接口,将配置数据逐字节的写入CPLD的寄存器中。以MIPS系列CPU XLS408为例,XLS408工作时钟频率为66.7 MHz,写总线周期最快需要10个工作时钟周期,即6.67 MHz,这一步受局部总线速度限制。

数据写入到CPLD后,再通过接口④——CPLD与FPGA之间的从并接口,将数据加载到FPGA,从并接口是同步总线,加载时间受限于总线时钟CCLK频率。

本方案的优点为:①、②两条路径可以在加载之前处理,且运行速度快,不占用加载时间。加载时间只受③、④的限制,而③受限于写总线周期间隔,④受限于从并接口的时钟。

3.2程序实现

CPLD从并程序采用verilog语言实现,该加载模块接口定义如下:

程序实现流如图3所示。

图3基于CPLD从并加载FPGA的程序流程

FPGA加载片选和写信号产生部分代码如下:

4仿真及加载结果分析

基于modelsim 6.5SE仿真波形可以看出CPU每加载1字节数据需要向CPLD写1次加载数据,这共需花费一个局部总线周期,局部总线频率最快为6.67 MHz.因此CPU加载4.125 MB数据到CPLD共需时间为:

CPLD需要1个CCLK周期写1字节数据到FPGA,CCLK则是利用CPU局部总线的写信号产生,可以实现CCLK和数据的同步,因此CCLK时钟速率为6.67 MHz,因此加载4.125 MB数据到FPGA,共需时间为:

FPGA上电需要1 ms,因此当FPGA使用SPARTAN-6系列最高端的6SLX150T时,采用基于CPLD的从并加载方式,共需要的加载时间为1.221 s,满足通信产品FPGA加载时间小于2 s的要求。而如果采用从串等加载方式,使用ARM7处理器作为控制器,对于CycloneII系列中的EP2C35,配置文件大小1.16 MB,加载时间需要1.30 min;采用基于CPLD的从串加载方式,加载同样4.125 MB的FPGA数据,CPLD加载时钟33MHz,则加载时间需要3.8 s,FPGA加载时间过长,则会影响系统的启动时间。

表2是常用加载方式加载6SLX150T型号FPGA芯片数据所需时间比较。

表2 FPGA加载时间对比

从上述分析可以得出结论,如果提高CPU的局部总线写速度,加载FPGA的时间就会更快。

5结束语

使用基于CPLD的FPGA从并加载方案,相对于其它几种加载方式,虽然加载管脚增多,但加载时间大大缩短,并且如果提高CPU局部总线的写速度,加载速度有进一步提高空间,满足通信系统快速启动的要求,具有很高的实用价值。

FPGA 集成电路 电路 总线 Xilinx CPLD MIPS 仿真 ARM 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)