基于FPGA与VHDL的微型打印机的驱动设计

时间:11-04

来源:互联网

点击:

引 言

FPGA 即现场可编程逻辑阵列。是在CPLD 的基础上发展起来的新型高性能可编程逻辑器件。FPGA的集成度很高,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。新一代的FPGA 甚至集成了中央处理器( CPU ) 或数字处理器( DSP) 内核,在一片FPGA 上进行软硬件协同设计,为实现片上可编程系统( SOPC) 提供了强大的硬件支持。对微型打印机的驱动,传统方法是使用单片机是实现对其的时序控制。随着FPGA 在各领域的普及使用,以及对微型打印机的需要,因此要实现FPGA 对微型打印机的时序控制。

当前各ASIC 芯片制造商都相继开发了用于各自目的的HDL 语言,但是大多数都为标准化和通用化。惟一被公认的是美国国防部开发的VHDL 语言,它已成为IEEE ST D_1076 标准。另外从近期HDL语言发展的动态来看,许多公司研制的硬件电路设计工具业都逐渐向VHDL 语言靠拢,使得他们的硬件电路设计工具也能支持VHDL 语言。

VHDL 语言可以支持自上而下和基于库的设计方法,而且还支持FPGA 的设计。

1 微型打印机简介

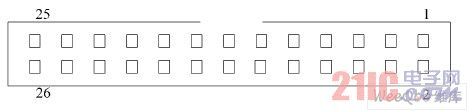

RD DH 型微型打印机采用热敏加热点阵打印方式,是一款体积小,打印速度快的打印输出设备。该型打印机可采用标准并行接口,RS 232 串行接口,T TL电平串口,485 接口,USB 接口,打印速度达到50 m/ s,分辨率为8 点/ mm,384 点/ 行,打印纸张采用57 mm热敏纸。可打印国标一、二级汉字库中全部汉字和西文字、图标共8 178 个。微型打印机并行接口与CENTRONICS标准接口兼容,可直接由微机并口或单片机控制。其26 线双排插座引脚序号如图1 所示。此26 个并口各引脚信号定义如表1 所示。

图1 双排插座引脚序号

表1 微型打印机26 并口各引脚定义

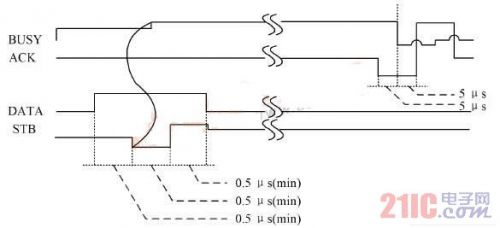

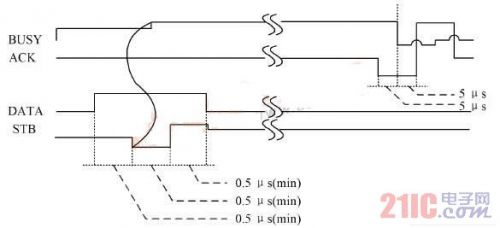

对打印机的驱动主要是对其工作时序进行正确的控制,RD DH 型并行接口定时图如图2 所示。

图2 并行接口定时图

2 总体系统设计

使用Altera 公司的Cyclon ?系列的FPGA 芯片EP3C25Q240C8N 实现对RD DH 型微型打印机的硬件电路控制,使用Quar tus 开发工具,通过VHDL 语言实现对微型打印机的软件功能实现。

2. 1 硬件电路设计

如图3 所示为打印机与FPGA 的连接示意图。

DATA 1~ DATA8 表示打印机的8 个数据位,他们的逻辑“1”表示高电平,逻辑“0”表示低电平; STB 为数据选通触发脉冲,下降沿时读入数据; ACK 为回答脉冲,低电平表示数据已被接受; BUSY 为高电平时表示打印机正忙,此时不接收数据。

由于 ACK 和BUSY 输出的是5 V 的TT L 电平,而FPGA 的I/ O 口标准为3. 3 V LVCMOS 电平,因此这两个信号作为FPGA 的输入信号时,要进行分压,保证电路正常运行。

图3 FPGA 与打印机连接示意图

2. 2 软件设计

软件平台采用Altera 公司的FPGA 开发平台Quartus 。

Quartus 提供了一种与器件结构无关的设计环境,设计者不需要精通器件的内部结构,只需要运用自己熟悉的输入工具( 如原理图输入或数字电路描述语言输入) 进行设计,利用Quar tus 可以将这些设计转换为最终结构所需要的格式。有关结构的详细知识已写入开发工具软件,设计人员无需手工优化自己的设计。软件的开发流程如图4 所示。

图4 软件开发流程图

使用VHDL 硬件描述语言来进行软件设计。

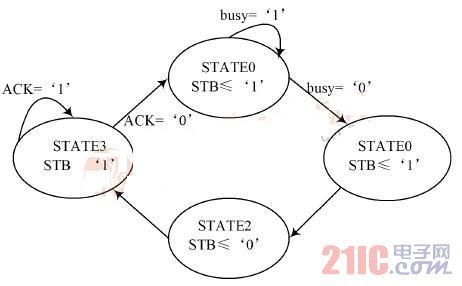

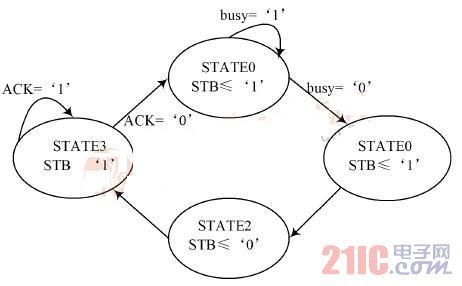

对微型打印机的驱动主要是对其工作时序进行正确的控制,利用VHDL 常见的状态机来实现对打印机的工作时序的控制,根据时序图1 所示的时序,状态机使用4 个状态,状态转换图如图5 所示。

初始状态STA TE0 时,数据选通触发脉冲信号STB 置“1” ( 高电平) ,检测打印机是否正忙,如果打印机为空闲状态( busy= “0”) ,转入下一状态STAT E1,否则( busy = “1 ” ) 继续执行ST AT E0; 在状态STAT E1,将数据写入打印机,直接转入下一状态; 在状态STAT E2,将数据选通触发脉冲信号STB 置“0” ,打印机读数据,转入下一状态; 在状态ST ATE3,检测数据是否已经被接受,若数据已被接受( ACK = “0” ) ,打印机转入初始状态ST AT E0,等待接受新数据,若数据未被接受( ACK = “1” ) ,继续执行STAT E3 直到数据被接受。

图5 状态转换图

3 结 语

使用FPGA 与V HDL 硬件描述语言设计的微型打印机驱动,通过系统调试能够完成对打印机的时序控制,目前已经在某型测试仪中正常使用。该设计系统控制简单,抗干扰性强,可靠性高,移植性较好,能够用于任何使用FPGA 芯片的系统中,具有一定的应用前景。

FPGA 即现场可编程逻辑阵列。是在CPLD 的基础上发展起来的新型高性能可编程逻辑器件。FPGA的集成度很高,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与组合逻辑电路功能,适用于高速、高密度的高端数字逻辑电路设计领域。新一代的FPGA 甚至集成了中央处理器( CPU ) 或数字处理器( DSP) 内核,在一片FPGA 上进行软硬件协同设计,为实现片上可编程系统( SOPC) 提供了强大的硬件支持。对微型打印机的驱动,传统方法是使用单片机是实现对其的时序控制。随着FPGA 在各领域的普及使用,以及对微型打印机的需要,因此要实现FPGA 对微型打印机的时序控制。

当前各ASIC 芯片制造商都相继开发了用于各自目的的HDL 语言,但是大多数都为标准化和通用化。惟一被公认的是美国国防部开发的VHDL 语言,它已成为IEEE ST D_1076 标准。另外从近期HDL语言发展的动态来看,许多公司研制的硬件电路设计工具业都逐渐向VHDL 语言靠拢,使得他们的硬件电路设计工具也能支持VHDL 语言。

VHDL 语言可以支持自上而下和基于库的设计方法,而且还支持FPGA 的设计。

1 微型打印机简介

RD DH 型微型打印机采用热敏加热点阵打印方式,是一款体积小,打印速度快的打印输出设备。该型打印机可采用标准并行接口,RS 232 串行接口,T TL电平串口,485 接口,USB 接口,打印速度达到50 m/ s,分辨率为8 点/ mm,384 点/ 行,打印纸张采用57 mm热敏纸。可打印国标一、二级汉字库中全部汉字和西文字、图标共8 178 个。微型打印机并行接口与CENTRONICS标准接口兼容,可直接由微机并口或单片机控制。其26 线双排插座引脚序号如图1 所示。此26 个并口各引脚信号定义如表1 所示。

图1 双排插座引脚序号

表1 微型打印机26 并口各引脚定义

对打印机的驱动主要是对其工作时序进行正确的控制,RD DH 型并行接口定时图如图2 所示。

图2 并行接口定时图

2 总体系统设计

使用Altera 公司的Cyclon ?系列的FPGA 芯片EP3C25Q240C8N 实现对RD DH 型微型打印机的硬件电路控制,使用Quar tus 开发工具,通过VHDL 语言实现对微型打印机的软件功能实现。

2. 1 硬件电路设计

如图3 所示为打印机与FPGA 的连接示意图。

DATA 1~ DATA8 表示打印机的8 个数据位,他们的逻辑“1”表示高电平,逻辑“0”表示低电平; STB 为数据选通触发脉冲,下降沿时读入数据; ACK 为回答脉冲,低电平表示数据已被接受; BUSY 为高电平时表示打印机正忙,此时不接收数据。

由于 ACK 和BUSY 输出的是5 V 的TT L 电平,而FPGA 的I/ O 口标准为3. 3 V LVCMOS 电平,因此这两个信号作为FPGA 的输入信号时,要进行分压,保证电路正常运行。

图3 FPGA 与打印机连接示意图

2. 2 软件设计

软件平台采用Altera 公司的FPGA 开发平台Quartus 。

Quartus 提供了一种与器件结构无关的设计环境,设计者不需要精通器件的内部结构,只需要运用自己熟悉的输入工具( 如原理图输入或数字电路描述语言输入) 进行设计,利用Quar tus 可以将这些设计转换为最终结构所需要的格式。有关结构的详细知识已写入开发工具软件,设计人员无需手工优化自己的设计。软件的开发流程如图4 所示。

图4 软件开发流程图

使用VHDL 硬件描述语言来进行软件设计。

对微型打印机的驱动主要是对其工作时序进行正确的控制,利用VHDL 常见的状态机来实现对打印机的工作时序的控制,根据时序图1 所示的时序,状态机使用4 个状态,状态转换图如图5 所示。

初始状态STA TE0 时,数据选通触发脉冲信号STB 置“1” ( 高电平) ,检测打印机是否正忙,如果打印机为空闲状态( busy= “0”) ,转入下一状态STAT E1,否则( busy = “1 ” ) 继续执行ST AT E0; 在状态STAT E1,将数据写入打印机,直接转入下一状态; 在状态STAT E2,将数据选通触发脉冲信号STB 置“0” ,打印机读数据,转入下一状态; 在状态ST ATE3,检测数据是否已经被接受,若数据已被接受( ACK = “0” ) ,打印机转入初始状态ST AT E0,等待接受新数据,若数据未被接受( ACK = “1” ) ,继续执行STAT E3 直到数据被接受。

图5 状态转换图

3 结 语

使用FPGA 与V HDL 硬件描述语言设计的微型打印机驱动,通过系统调试能够完成对打印机的时序控制,目前已经在某型测试仪中正常使用。该设计系统控制简单,抗干扰性强,可靠性高,移植性较好,能够用于任何使用FPGA 芯片的系统中,具有一定的应用前景。

FPGA CPLD 电路 DSP 单片机 VHDL USB Altera CMOS Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)