FPGA实战演练逻辑篇60:VGA驱动接口时序设计之7优化

时间:08-10

来源:互联网

点击:

VGA驱动接口时序设计之7优化

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

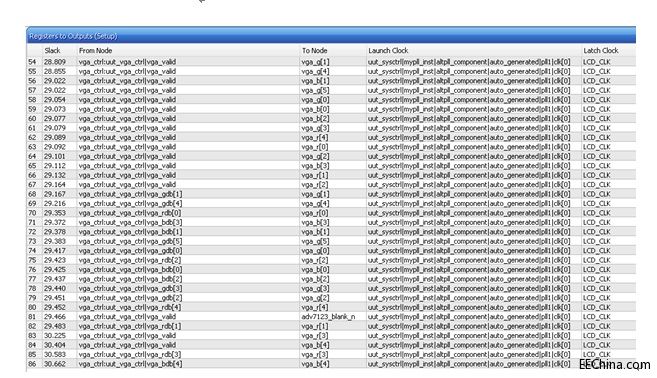

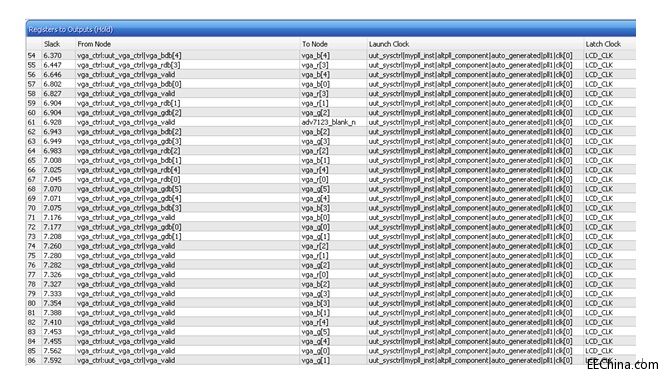

最后,再次编译系统,查看时序报告。如图8.41和图8.42所示,我们看到数据总线的Setup和Hold时间的余量都很充足,这样看来,我们的设计达到了时序收敛的目的。(特权同学,版权所有)

图8.41 setup时间时序分析报告

图8.42 hold时间时序分析报告

为了帮助大家进一步的理解时序的概念,这里可以找一条路径,将他们的建立时间和保持时间波形图同时拉出来,如图8.43所示,大家便可一目了然。建立时间和保持时间会分别使用他们最坏的情况进行分析,然后得出相应的时序余量。左图的竖线条是时钟的latch沿,我们看在它前面9.713ns数据都是保持稳定的,完全满足ADV7123芯片datasheet上的0.2ns建立时间要求;右图的竖线条是保持时间的latch沿,它和launch沿是对齐的,我们看到它以后大约3.9ns数据才会发生变化,也完全满足ADV7123芯片datasheet上的1.5ns保持时间要求。(特权同学,版权所有)

图8.43 某路径的setup时间和hold时间波形示意图

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)