FPGA实战演练逻辑篇50:时钟

时钟

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

下面我们再来对时序分析的一些最基本概念及其相互关系进行探讨,即时钟和建立时间、保持时间的关系。(特权同学,版权所有)

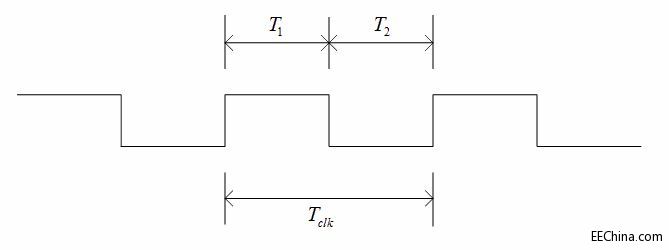

时钟这个并不陌生的词汇,无需大做文章,就先举个最典型的时钟模型献给大家。如图8.7所示,理想的时钟模型是一个占空比为50%且周期固定的方波。Tclk为一个时钟周期,T1为高脉冲宽度,T2为低脉冲宽度,Tclk=T1+T2。占空比定义为高脉冲宽度与周期之比,即T1/Tclk。(特权同学,版权所有)

图8.7 时钟基本模型

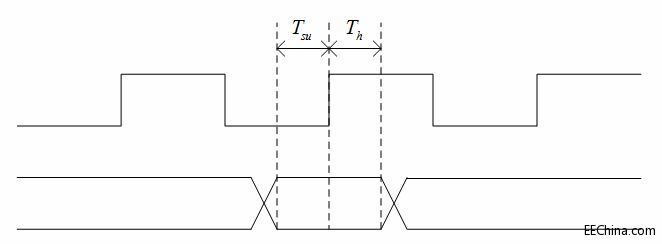

所谓建立时间(Tsu),是指在时钟上升沿到来之前数据必须保持稳定的时间;所谓保持时间(Th),是指在时钟上升沿到来以后数据必须保持稳定的时间。一个数据需要在时钟的上升沿被锁存,那么这个数据就必须在这个时钟上升沿的建立时间和保持时间内保持稳定。换句话说,就是在这段时间内传输的数据不能发生任何的变化。时钟沿与建立时间和保持时间之间的关系如图8.8所示。(特权同学,版权所有)

图8.8 时钟沿与建立时间和保持时间之间的关系

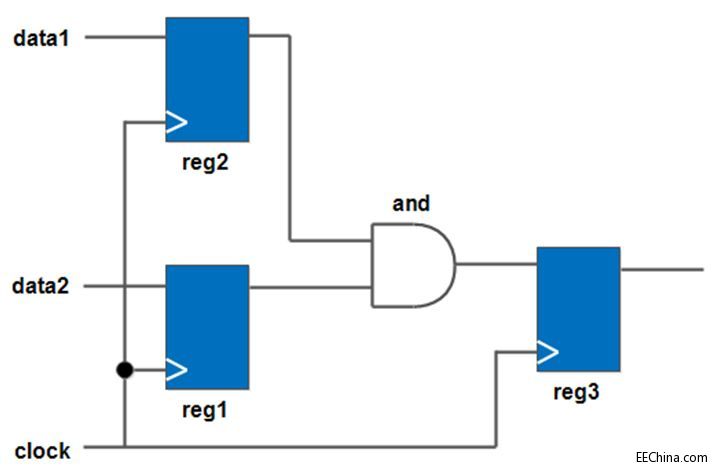

这里,我们举一个二输入与功能的时序设计模型,如图8.9所示。输入数据data1和data2会在时钟的上升沿被分别锁存到reg2和reg1的输出端,然后这两个信号分别经过各自的路径到达与门and的输入端,他们相与运算后信号传送到下一级寄存器reg3的输入端,对应他们上一次被锁存后的下一个时钟上升沿,reg3的输入端数据被锁存到了输出端。这个过程是一个典型的寄存器到寄存器的数据传输。下面我们就要以此为基础来探讨他们需要满足的建立时间和保持时间的关系。(特权同学,版权所有)

图8.9 二输入与功能的寄存器模型

如图8.10的波形所示,clk表示时钟源发出的时钟波形,它要分别达到上面例子中的源寄存器reg1和reg2,以及达到目的寄存器reg3,所经过的时间是不一样的,因此我们看到波形中给出的时钟到达reg3的波形clk_r3相对于基准时钟clk的波形会略有一些偏差(稍微延时一些,这是真实情况的模拟)。reg1out和reg2out分别是数据data1和data2被锁存到各自寄存器的输出端的波形,reg3in则是reg1out和reg2out的波形经过路径延时和门延时后到达reg3in的波形,而reg3out则是在clk_r3的上升沿来到并锁存好有效的数据后,其寄存器输出端的波形。(特权同学,版权所有)

FPGA 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)