FPGA实战演练逻辑篇65:CMOS摄像头接口时序设计5时序报告

时间:08-19

来源:互联网

点击:

CMOS摄像头接口时序设计5时序报告(特权同学版权所有)

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

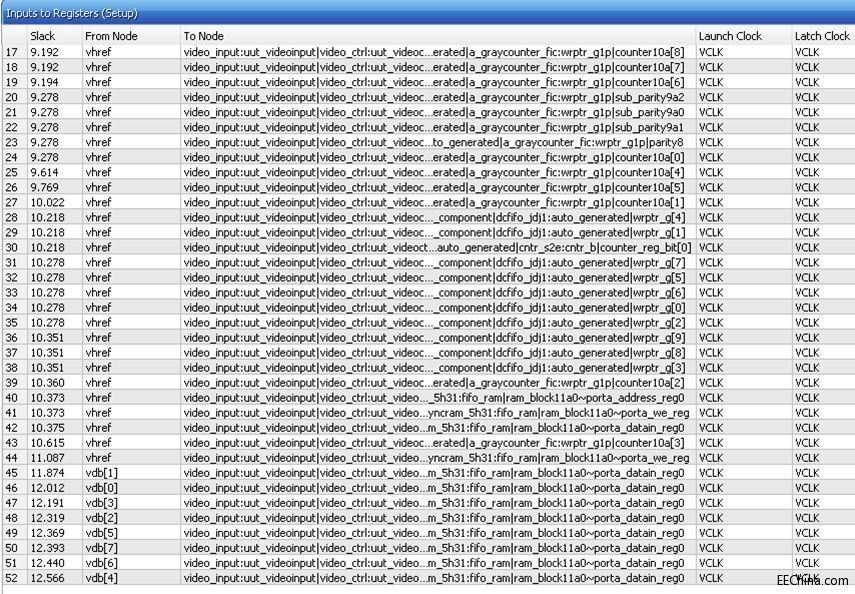

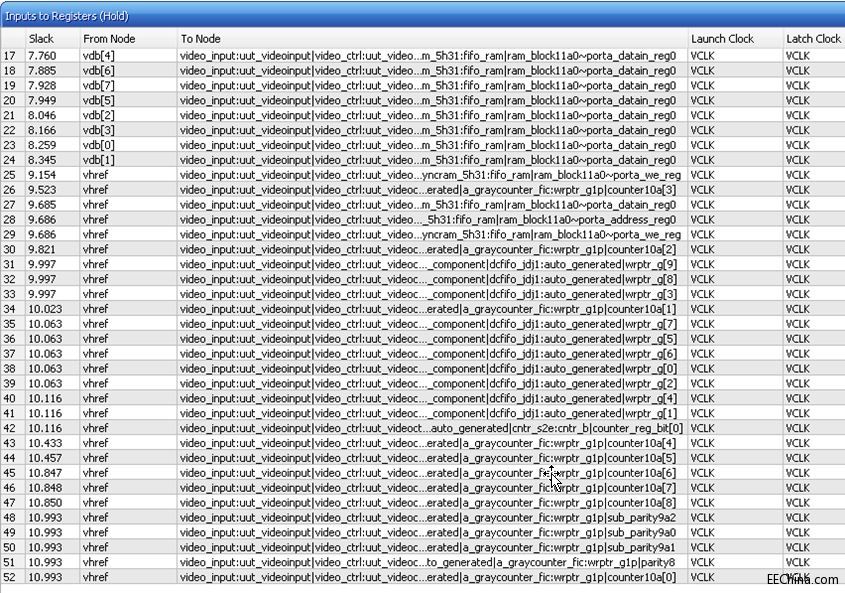

约束完成后,参照前面章节Update Timing Netlist并且Write SDC File…,接着就可以重新编译整个工程,再来看看这个时序分析的报告。如图8.57和图8.58所示,在报告中,数据的建立时间有9~13ns的余量,而保持时间也都有7~11ns的余量,可谓余量充足。(特权同学,版权所有)

图8.57 setup时序报告

图8.58 hold时序报告

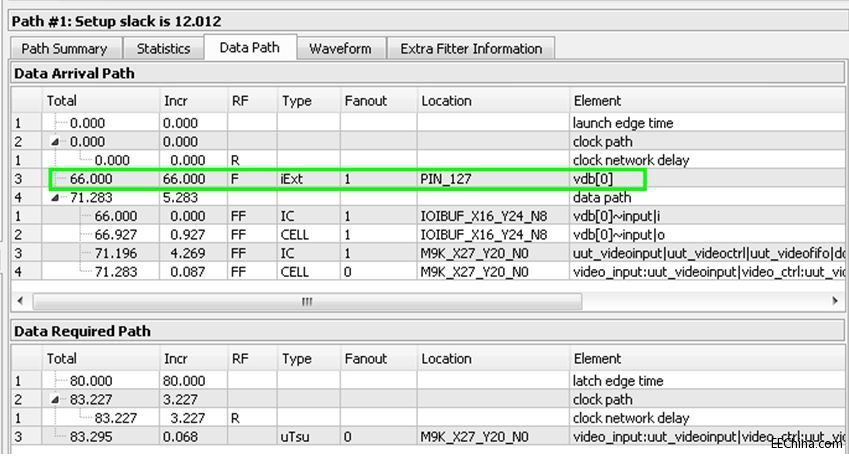

另外,我们也可以专门找一条路径出来,看看它的具体时序路径的分析。如图8.59所示,vd[0]这条数据线的建立时间报告中,66ns的input max delay出现在了Data Arrival Path中。(特权同学,版权所有)

图8.59 vd[0]路径的setup时序报告

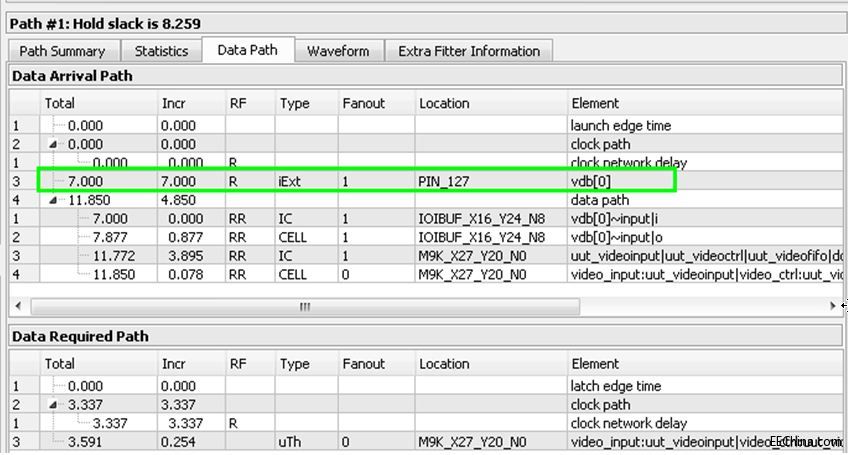

而在vd[0]的保持时间报告中,如图8.60所示,7ns的input min delay则出现在了Data Arrival Path中。(特权同学,版权所有)

图8.60 vd[0]路径的hold时序报告

- 适用于消费性市场的nano FPGA技术(09-27)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- FPGA中嵌入式存储器模块的设计(03-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)

- FPGA控制CLC5958型A/D转换器高速PCI采集(06-08)