FPGA实战演练逻辑篇64:CMOS摄像头接口时序设计4时序约束

时间:08-18

来源:互联网

点击:

CMOS摄像头接口时序设计4时序约束(特权同学版权所有)

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》(特权同学版权所有)

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

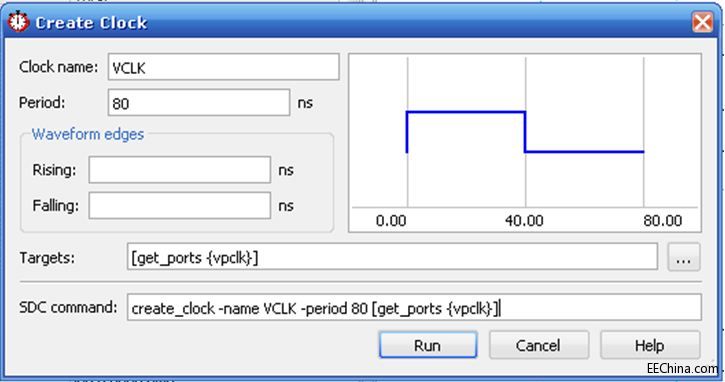

下面我们来添加时序约束,打开TimeQuest,点击菜单栏的ContraintsàCreat Clock,做如图8.54所示的设置,首先约束CMOS Sensor的同步时钟VCLK。(特权同学,版权所有)

图8.54 VCLK时钟约束

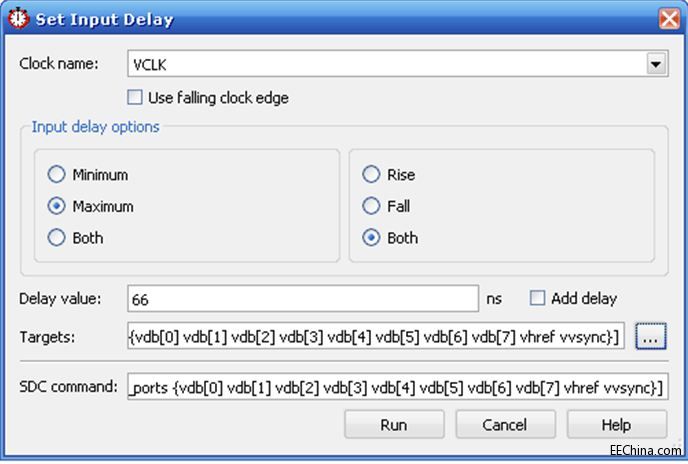

点击ContraintsàSet Maximum Delay,对vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_max_delay做如图8.55所示的设置。(特权同学,版权所有)

图8.55 set_max_delay约束

点击ContraintsàSet Minimum Delay,对vdb[0] vdb[1] vdb[2] vdb[3] vdb[4] vdb[5] vdb[6] vdb[7] vhref的set_min_delay做如图8.56所示的设置。(特权同学,版权所有)

图8.56 set_min_delay约束

- 适用于消费性市场的nano FPGA技术(09-27)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- FPGA中嵌入式存储器模块的设计(03-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)

- FPGA控制CLC5958型A/D转换器高速PCI采集(06-08)