FPGA实战演练逻辑篇32:摄像头与超声波接口概述

摄像头与超声波接口概述

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

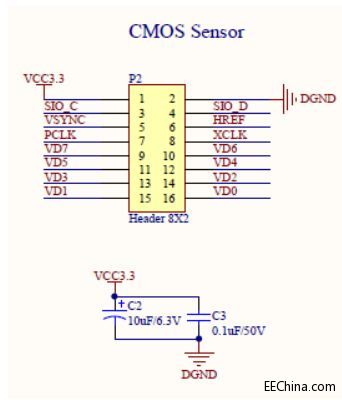

视频采集模块上板载了一颗CMOSSensor,该模块预留了16PIN的插针接口,对应连接到SF-SENSOR子板的P2插座上,P2插座的电路如图3.74所示。(特权同学,版权所有)

图3.74 视频采集模块接口电路

P2插座上各个引脚的定义如表3.11所示。(特权同学,版权所有)

表3.11 视频采集模块接口引脚功能定义

| 引脚 | 信号 | 功能 |

1 | VCC3.3 | 电源电压3.3V。 |

2 | DGND | 电源地。 |

3 | SIO_C | 用于配置CMOS Sensor芯片内部寄存器的I2C接口时钟信号。 |

4 | SIO_D | 用于配置CMOS Sensor芯片内部寄存器的I2C接口数据信号。 |

5 | VSYNC | 伴随视频数据输出的场同步信号。 |

6 | HREF | 伴随视频数据输出的行同步信号。 |

7 | PCLK | 用于视频数据总线同步的时钟信号。 |

8 | XCLK | 外部(FPGA)输给CMOS Sensor芯片工作的时钟信号。 |

9 | VD7 | CMOS Sensor输出的视频数据总线。 |

10 | VD6 | CMOS Sensor输出的视频数据总线。 |

11 | VD5 | CMOS Sensor输出的视频数据总线。 |

12 | VD4 | CMOS Sensor输出的视频数据总线。 |

13 | VD3 | CMOS Sensor输出的视频数据总线。 |

14 | VD2 | CMOS Sensor输出的视频数据总线。 |

15 | VD1 | CMOS Sensor输出的视频数据总线。 |

16 | VD0 | CMOS Sensor输出的视频数据总线。 |

P4插座将用于超声波测距模块的连接,其电路如图3.75所示。(特权同学,版权所有)

图3.75 超声波模块接口电路

P4的4个引脚定义如表3.12所示。(特权同学,版权所有)

表3.12 超声波模块接口引脚功能定义

| 引脚 | 信号 | 功能 |

1 | VCC5 | 电源电压5V。 |

2 | TRIG | 超声波模块的触发输入信号。 |

3 | ECHO | 超声波模块的响应输出信号。 |

4 | DGND | 电源地。 |

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)