FPGA实战演练逻辑篇27:VGA显示驱动子板设计

VGA显示驱动子板设计

本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》

配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt

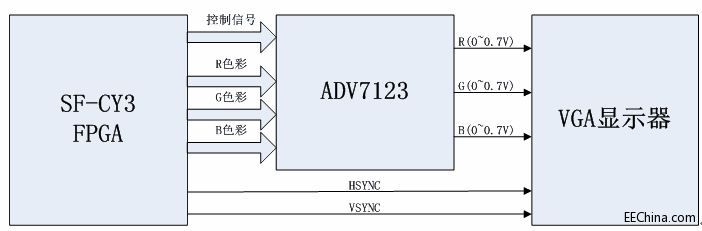

SF-VGA板载用于驱动VGA显示器的专用D/A转换芯片AVD7123,FPGA通过OUPLLN连接器驱动ADV7123芯片产生供给VGA显示器的色彩以及同步信号。SF-CY3核心板与SF-VGA子板模块连接的系统框图如图3.57所示。FPGA产生ADV7123的同步信号以及3组供给ADV7123内部3路并行D/A转换的数字信号,经过ADV7123的这3组VGA色彩数字信号最终转换为0~0.7V的模拟电压送给VGA显示器。而FPGA另外会产生用于同步色彩数据的场同步信号VSYNC和行同步信号HSYNC。(特权同学,版权所有)

图3.57 SF-CY3核心与SF-VGA子板模块连接的系统框图

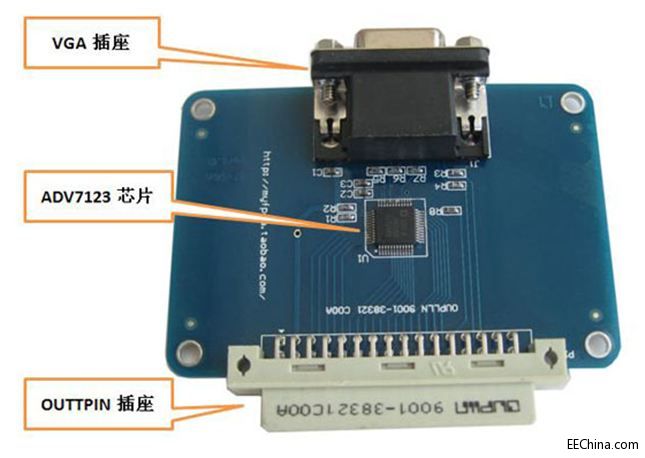

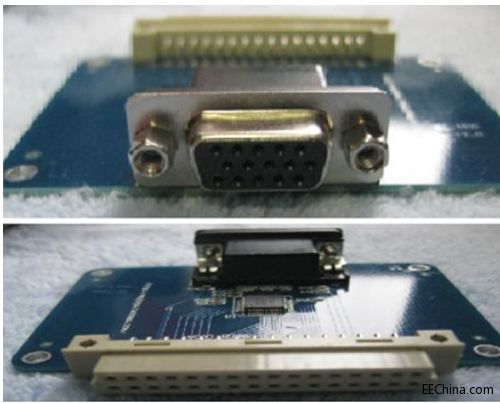

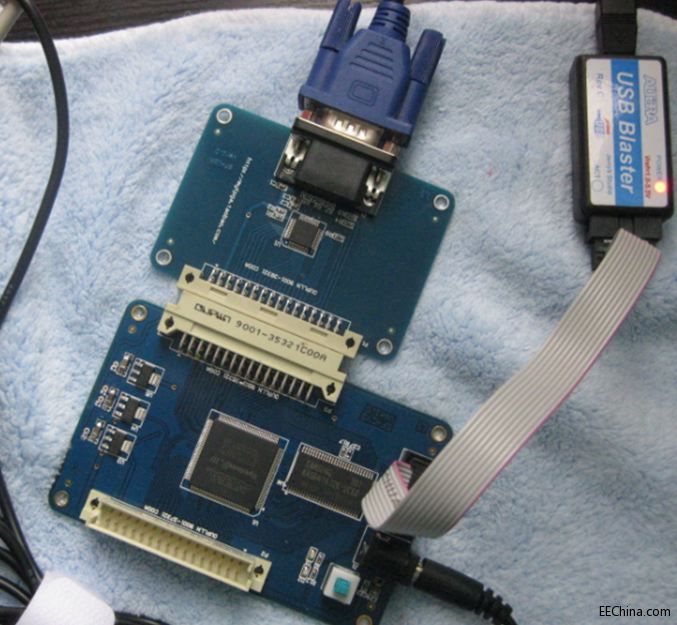

SF-VGA子板的实物图片如图3.58和图3.59所示。(特权同学,版权所有)

图3.58 SF-VGA子板实物照片1

图3.59 SF-VGA子板实物照片2

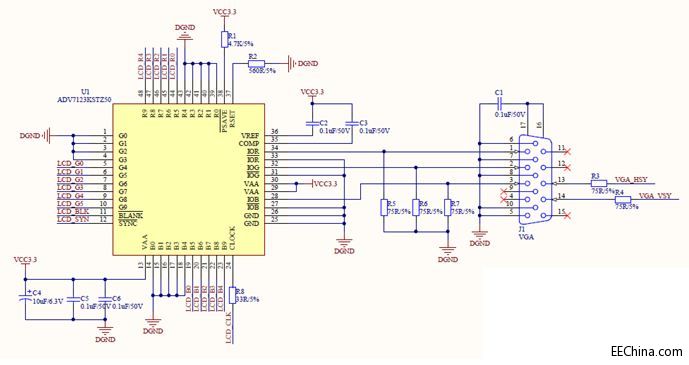

ADV7123芯片以及外围电路如图3.60所示。它的3路D/A信号实际上都是8bit位宽,但是我们只使用了565的RGB(即5bit的R信号,6bit的G信号,5bit的B信号)输出,所以把不使用的RGB信号都统一接地。用于同步数据传输的有时钟LCD_CLK、转换数据有效控制信号LCD_BLK和补偿同步控制信号LCD_SYN。根据datasheet,实际上LCD_SYN我们无需使用,所以逻辑驱动给他0电平就可以了。而LCD_CLK是和输出的数据总线同步的,根据我们所需要的显示驱动分辨率和刷新率决定,LCD_BLK信号则在数据总线有效时拉高即可。(特权同学,版权所有)

ADV7123的模拟输出IOR、IOG、IOB信号直接连接到VGA插座上,同时FPGA输出的两个同步信号VGA_HSY和VGA_VSY也直接连接到VGA插座上。(特权同学,版权所有)

图3.60ADV7125与VGA接口电路

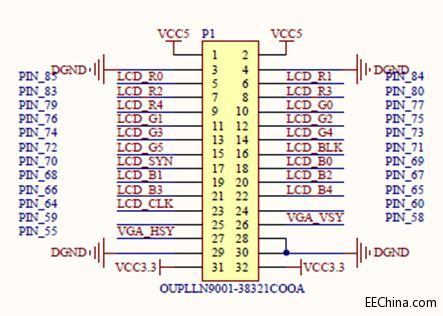

SF-VGA子板上用于连接SF-CY3核心板的连接器电路如图3.61所示。(特权同学,版权所有)

图3.61 SF-VGA子板与FPGA的连接插座电路

SF-VGA与FPGA引脚定义如表3.6所示。(特权同学,版权所有)

表3.6 SF-VGA与FPGA引脚定义

| 分类 | 名称 | 引脚号 | 功能描述 |

VGA数据信号 | LCD_R0 | 85 | 红色数据位0。 |

| LCD_R1 | 84 | 红色数据位1。 |

| LCD_R2 | 83 | 红色数据位2。 |

| LCD_R3 | 80 | 红色数据位3。 |

| LCD_R4 | 79 | 红色数据位4。 |

| LCD_G0 | 77 | 绿色数据位0。 |

| LCD_G1 | 76 | 绿色数据位1。 |

| LCD_G2 | 75 | 绿色数据位2。 |

| LCD_G3 | 74 | 绿色数据位3。 |

| LCD_G4 | 73 | 绿色数据位4。 |

| LCD_G5 | 72 | 绿色数据位5。 |

| LCD_B0 | 69 | 蓝色数据位0。 |

| LCD_B1 | 68 | 蓝色数据位1。 |

| LCD_B2 | 67 | 蓝色数据位2。 |

| LCD_B3 | 66 | 蓝色数据位3。 |

| LCD_B4 | 65 | 蓝色数据位4。 |

VGA同步信号 | VGA_VSY | 58 | 场同步信号。 |

| VGA_HSY | 55 | 行同步信号。 |

A/D控制信号 | LCD_CLK | 64 | 数据同步时钟信号。 |

| LCD_BLK | 71 | 转换数据有效控制信号。 |

| LCD_SYN | 70 | 补偿同步控制信号。 |

SF-VGA子板的OUPLLN插座P1连接SF-CY3核心板的插座P3,其实物连接如图3.62所示。(特权同学,版权所有)

图3.62 SF-VGA子板与SF-CY3核心板的实物连接

FPGA 显示器 连接器 电压 电路 LCD 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)