FPGA入门:第一个工程实例之功能概述

FPGA入门:第一个工程实例之功能概述

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

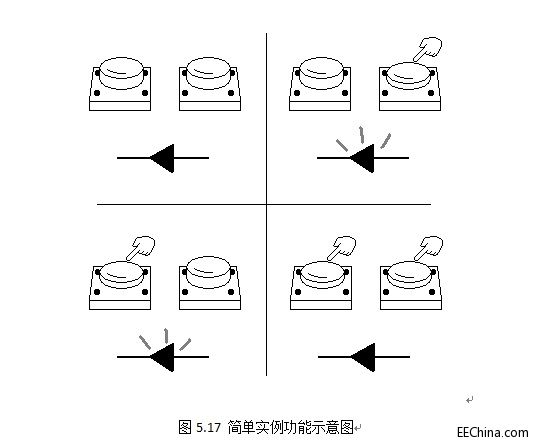

下面我们将以一个简单的实例开始带大家熟悉可编程逻辑设计的开发流程。在这个实例当中,我们将用到开发板上的两个按键和一个LED指示灯。如图5.17所示,两个按键在所有可能的四种组合状态下,其控制的LED指示灯状态如下:

● 没有手指触碰按键,LED灭;

● 手指按下左边按键,LED亮;

● 手指按下右边按键,LED亮;

● 手指同时按下两个按键,LED灭。

图5.17 简单实例功能示意图

把这个实例的两个按键作为输入,LED指示灯作为输出,不难得到如表5.1所示的真值表。在该真值表中,按键未被按下时为高电平,取值1;按键按下时为低电平,取值0。连接LED指示灯的IO输出高电平,即值1时,LED指示灯亮;输出低电平,即值0时,LED指示灯灭。

表5.1 按键输入与LED输出真值表

| 按键左 | 按键右 | LED指示灯 |

1 | 1 | 0 |

0 | 1 | 1 |

1 | 0 | 1 |

0 | 0 | 0 |

如果用门逻辑表示该真值表,其关系如下:

LED指示灯状态 = 按键左的键值异或 按键右的键值

明白了这个关系后,我们下面就可以开始一步步的着手把这个简单得不能再简单的功能实现到最终的实验板上。注意这个简单实例的目的不在于功能本身,而是要利用它让大家熟悉开发的流程。

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

FPGA CPLD Verilog VHDL LED 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)