FPGA入门:第一个工程实例之功能仿真运行

FPGA入门:第一个工程实例之功能仿真运行

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

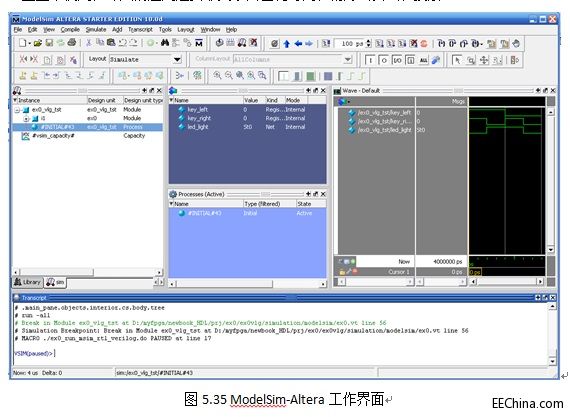

仿真测试的所有准备工作就绪了,下面我们就可以一键完成仿真工作。点击菜单栏的ToolsàRun Simulation ToolàRTL Simulation。随后ModelSim-Altera便启动,如图5.35所示,这是ModelSim-Altera软件的工作界面。关于ModelSim-Altera软件的基本使用建议大家参考该软件菜单栏Help下自带的一些文档,尤其是HelpàPDF Documentation里的几个文档。ModelSim-Altera的功能也非常强大实用,如果要详细展开来探讨,恐怕也要专门写本书才可以。限于篇幅,本书也只能是简单的在工程需要时附带的和大家介绍ModelSim-Altera的一些基本使用,深入的应用还要靠大家自己花时间和精力去实践和摸索。

图5.35 ModelSim-Altera工作界面

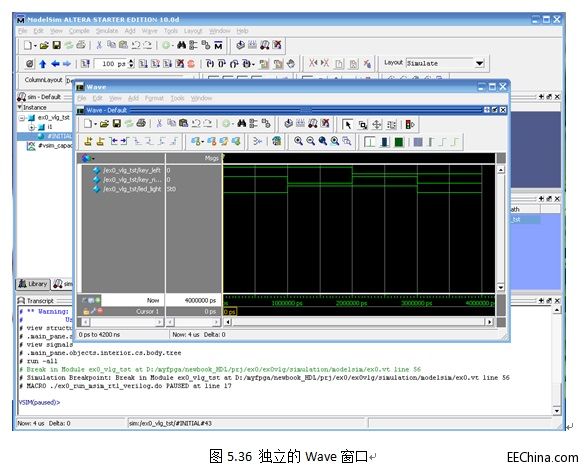

因为在Quartus II里,我们做了大量的工作,包括ModelSim-Altera仿真运行所需的各类文件,主要是被测试代码和测试脚本,那么当我们调用ModelSim-Altera软件时,它一方面要自动的将Altera器件的库进行编译,另一方面则会对前面所说的几个设计文件进行编译和运行,运行的对象当然是基于我们的测试脚本文件(*.vt)。在Wave窗口里,测试脚本的3个主要信号key_left、key_right和led_light的波形已经产生了。我们可以通过点击Wave窗口右上角的Dock/Undock按钮(即打向右上角箭头那个图标)将其进行独立显示,如图5.36所示。

图5.36 独立的Wave窗口

如图5.37所示,这里的3个顶层信号key_left、left_right和led_light都在仿真波形中显示出来了。正如我们在测试脚本里面所控制的,在0-1000ns时,key_left = 1和key_right = 1;在1000-2000ns时,key_left = 1和key_right = 0;在2000-3000ns时,key_left = 0和key_right = 1;在3000-4000ns时,key_left = 0和key_right = 0。而输出信号led_light的结果为:0-1000ns和3000-4000ns值为0,1000-3000ns值为1。这样的结果正好满足设计代码里的输入输出关系:LED指示灯状态 = 按键左的键值异或 按键右的键值。

图5.37 ex0仿真波形

从仿真波形结果上,验证了我们设计代码是正确的,功能已经实现。

本文节选自特权同学的图书《FPGA/CPLD边练边学——快速入门Verilog/VHDL》

书中代码请访问网盘:http://pan.baidu.com/s/1bndF0bt

FPGA 仿真 CPLD Verilog VHDL ModelSim Altera Quartus LED 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)