基于FPGA和LCOS技术的3D视频前端处理与显示系统设计

时间:02-06

来源:互联网

点击:

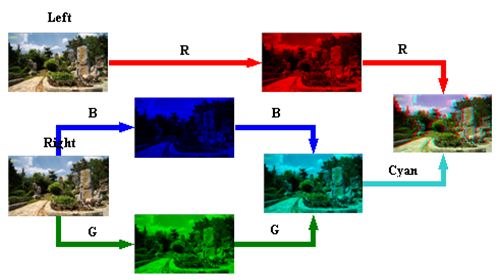

目前,3D显示已逐渐融入到人们的生活当中,因其能再现真实的三维场景,受到了人们的广泛热爱,红蓝3D图像获取的基本原理如图1所示。摄像头采集同一场景的两路视频图像信号,对其中一路信号只提取图像信号的红色分量;另一路提取图像信号的蓝、绿色合成的青色分量。将两路信号采用同步色差合成算法合成红蓝3D视频图像。目前国内3D电视产业面临的主要问题在于:(1)3D电视芯片的缺少而导致3D片源的短缺;(2)视频处理的复杂度较高;(3)显示与观看效果不佳。为此本文对传统的视频处理过程中色度分量的提取、亮度的增强、红蓝3D眼镜的设计等方面进行了改进,并采用LCOS作为微显示器件,投影出红蓝3D视频图像。

图1 红蓝3D图像获取基本原理

1 颜色分量的获取与亮度的增强

传统的方法只采用红加蓝、红加绿色度分量合成3D视频,这样会使画面的损伤较大,丢失33%以上的颜色分量,观看起来颜色失真较大,亮度也大大降低,增加了眼睛的负担,易产生疲劳。针对颜色失真本文采用红加青的方法以减少色度的丢失,这样可使画面色度饱和度还原到原始画面的90%以上。

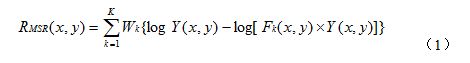

针对亮度降低提出了基于亮度的图像增强方法。传统的基于Retinex理论的演变法存在一定的不足,如将RGB空间转换到HSI空间需要大量的三角函数运算,并采用傅里叶变换处理Retinex理论部分的高斯函数,大大影响处理速度。本文提出了基于YCbCr颜色空间的亮度分量处理法,同时采用无限脉冲响应数字滤波器(IIR)实现高斯函数运算。实验证明,该算法不但能增强图像的质量,还能有效避免Retinex算法中带来的光环效应,同时大大加快算法处理速度。基于亮度Y分量的Retinex 处理过程可表示为:

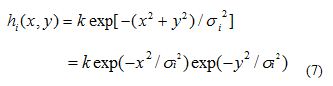

式中Y( x , y)为亮度分量函数,F( x , y) 被称为环境函数,一般用高斯函数表达式为:

σ为高斯函数的标准偏差,k 表示环境函数的个数。环境函数Fk用于选取不同的标准偏差σk,Wk用来控制环境函数范围的尺度,它表示与Fk相关的权重系数。

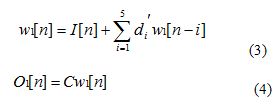

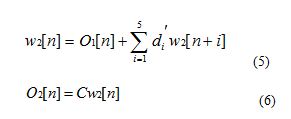

Retinex 处理算法的主要步骤就是高斯滤波,其运算速度直接决定了算法运行效率。为避免傅立叶变换的复杂的运算和不足,对高斯滤波器进行了IIR实现,把高斯滤波器分解为正向滤波器和反向滤波器的组合,如下面的差分方程。

正向滤波器:

其中,C、di’是滤波器系数,I [n]是输入数据,w1 [n]和w2 [n] 分别是正向和反向滤波器的中间状态,O1[n]、O2 [n]为其处理结果。正向和反向滤波器就构成了高斯滤波器的IIR实现过程。可以利用高斯函数的可分离性:

对图像先逐行后逐列进行处理,最终就可以实现二维高斯数字滤波。下图2为原图、传统Retinex算法、基于Y分量Retinex算法处理后的对比图。图中可以看出,传统算法可以增强图像亮度,但灰度化也很明显。而本文采用的方法不仅可以增强亮度,也可以保持原有图像的整体鲜艳效果。

(a)原图 (b)传统Retinex算法 (c)基于Y分量Retinex算法

图2 基于Y分量Retinex算法与传统Retinex算法的对比效果图

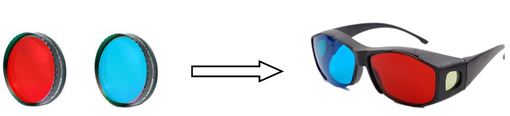

另外,传统的3D眼镜仅采用红色或蓝色塑料或玻璃镜片作为滤光片,使滤光效果大打折扣,观众佩戴观看影片时,会出现不同程度的重影现象,影响观看效果。为此本文采用反射率和透过率都达到90%以上的反青透红和反红透青的滤光片作为3D眼镜的镜片,这样可以使红色镜片仅通过红色画面,青色镜片透过蓝、绿色画面,消除了重影现象,使观看效果更加鲜活、逼真,下图3为滤光片及制作的红蓝3D眼镜。

图3 加滤光片红蓝3D眼镜

2 视频处理系统基本结构与简化

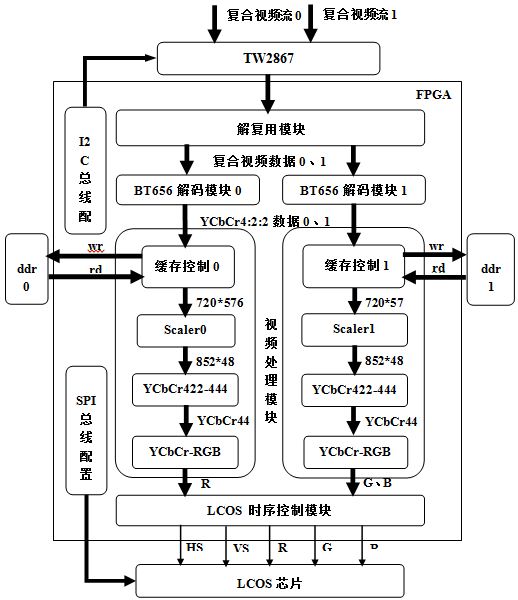

整个视频处理系统结构如图4所示。两路摄像头将采集到的信号送入TW2867进行A/D转换,输出的复用信号送入解复用(demux)模块,分离出的两路复合视频数据分别送入BT656数据解码模块、帧缓存控制模块、像素分辨率缩放模块、YCbCr 4:2:2转YCbCr 4:4:4数据模块、YCbCr亮度增强模块、YCbCr 4:4:4转RGB数据模块,最后将RGB数据送入LCOS时序控制模块,以镁光公司的CS-FLCOS作为微显示器件,搭建光机系统,显示出3D视频画面。对其中的TW2867芯片和LCOS芯片分别要进行I2C总线配置和SPI总线配置其内部的相关寄存器参数。

图4 3D显示系统框图

(1)TW2867解码

采用带有LED夜视功能的Sony CCD 感光芯片摄像头,视频输出分辨率为720*576,为标准的PAL制式视频格式。选用Techwell公司的TW2867 A/D转换芯片,能自动识别PAL/NTSC/SECAM格式的2路复合视频信号,通过I2C总线的配置,TW2867将两路摄像头信号转换为符合BT656标准的8位YCbCr数字信号。TW2867每一路都含有10位的ADC转换器、高质量的钳位和增益控制器和梳状滤波器,以滤除信号中的噪声,同时采用了一些图像增强技术,以获得高质量的YCbCr数字信号。

(2)BT656数据解码模块

国际电信联盟无线电通信组(ITU-CCIR)发布了ITU-BT656的视频标准,其行数据结构如图5所示。该模块首先需要检测数据流中是否按序出现了FF、00、00的帧头SAV或帧尾EAV信息。如果出现则对后8位的XY值进行判断,判断是否出现SAV、EAV信号,将有效视频信号的以亮度分量(Y)作为高8位,以色度分量(Cb或Cr)作为低8位合成16位的YCbCr数据,将BT656数据奇偶场的数据合并为一帧写入帧缓存中。

图5 BT. 656行数据结构

(3)像素分辨率缩放模块

帧缓存中装载的是两场视频数据,在读取的时候采用FIFO缓存并采用双线性插值算法,将原来720*576的像素分辨率放大到852*480。双线性插值算法将在水平和垂直两个方向分别进行一次线性插值。其定量计算方法如下:空间坐标系下四个点:A(x,y+1)、B(x,y)、C(x+1,y)、D(x+1,y+1),如图6所示,其灰度值依次为Ga、Gb、Gc、Gd,dx和dy分别表示目标点与点B在水平和垂直两个方向上的增量,其灰度值Gt可以由其余四点量化表示,如式2-1。

图6 双线性插值法示意图

Gt = (1 - dx)(1 - dy)Gb + dx(1 - dy)Gc + (1 - dx)dyGa + dxdyGd (2-1)

从电路实现方面而言,公式(2-1)共需要8个乘法器、2 个减法器和4 个加法器,将会占用较多的逻辑资源。将公式变形为:

Gt = Gb+dx(Gc-Gb)+dy(Ga-Gb)+dxdy(Gb-Ga-Gc+Gd)

= Gb+dx(Gc-Gb)+dy(Ga-Gb)+dxdy[(Gb-Ga)+(Gd-Gc)] (2-2)

公式(2-2)是另一种简化了电路的表示方法,仅需要4个乘法器、4 个减法器和3 个加法器。计算结果会有5个时钟周期的延时,当像素时钟为27Mhz,计算的时钟为一帧的数据转换为852*480*(1/27Mhz)=15ms,即可以实现实时的分辨率调整。

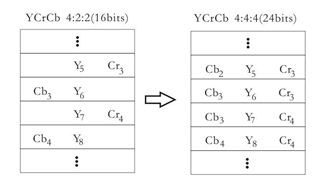

(4)YCbCr 4:2:2转YCbCr 4:4:4数据模块

将YCbCr4:4:4数据转换到YCbCr4:2:2是数字视频中的一个选通功能。而将YCbCr4:2:2数据转换到YCrCb4:4:4即是重采样的过程,采样的数据格式转变如图7所示。

图7 YCbCr422转YCbCr 444操作示意图

可知,输入16位YCbCr转换成了相应各8位Y、Cb、Cr信号,且输出像素采样率比输入采样率快了一倍,由此可见YCbCr4:2:2的数据格式压缩了将近一半的数据带宽。

(5)YCbCr444-RGB模块

将YCbCr数据转换为RGB数据可由下图8所示数据关系得到。由于FPGA进行浮点运算较为复杂,且占用的时钟周期较长(比如16位的浮点加法电路,一般多达十几到二三十个时钟周期),并不适合于实时视频数据处理,所以先通过对上式左右二端放大128倍化为整数运算,计算后再对结果除以128(右移7位),即可获得正确的结果。

图8 YCbCr444转RGB数据关系图

(6)LCOS时序控制模块

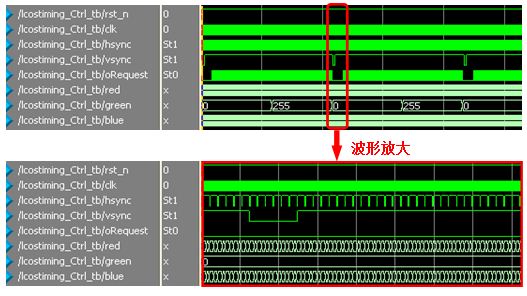

LCOS时序发生器主要用于产生微显示器件所需的时序,包括提供像素时钟(clk)、行同步信号(hsync)、场同步信号(vsync)、有效信号(valid),并输出当前行、列像素坐标值,从帧缓冲区发出数据请求信号并读出红、绿、蓝的视频数据。LCOS的时序仿真图如下图9所示。

图9 Modelsim中LCOS时序仿真图

3 FPGA红蓝3D视频获取及主观评价

FPGA选用的是Altera公司的Cyclone IV系列的EP4CE30F23C6N这款高速FPGA芯片,FPGA和DDR2之间的时钟频率可以达到200M,DDR2内部时钟频率达到400M,充分满足了两路视频处理的要求。通过对视频处理过程中模块的编写,编译后其消耗的的逻辑单元数为13615个,仅占总逻辑单元数的47%,如下图11所示,使视频处理过程更加简便高效。将以上各模块搭建、调试、下载到FPGA中,并采用镁光公司的LCOS芯片作为微显示器件,摄像头采集到的《阿凡达》2D电影的一个画面转换为3D换面效果如下图12所示,可以看到图面中的人物具有视差的红蓝两路图像,佩戴上红蓝3D眼镜,即可看到人物出屏的效果。

目前针对于3D显示的评价的方法主要还是主观的评价方法,按照2000年国际电信联盟发布的ITU-R BT.1438立体电视图像主观评价标准,分为5级,即优秀、良好、一般、不好、坏五个级别。以立体图片上的一点为中心,单眼左右移动时,图像会出现连续的跳跃,两次跳跃之间眼睛移动的角度为立体图像的视变角,视角越大,观看越舒适,但视角变大意味着立体感减弱。通过多人观看本文的3D视频,本设计主观评价在良好级别,达到了预期的设计效果。

图11 视频处理过程的硬件开销

图12 红蓝3D效果图

4 结束语

本文实现了一种结合Altera公司生产的Cyclone IV系列FPGA的3D视频前端处理与显示系统,具有设计周期短、结构简单、稳定可靠、实现效果逼真、节约设计成本的优点。高速图像采集系统中采用FPGA作为采集控制部分,不仅可以提高系统处理的速度,还可以提高系统的灵活性和适应性。弥补了当前3D电视芯片缺少的问题,对原有的视频处理过程及显示器件进行了改进,并提出了一种简便性和普适性的图像增强算法。该系统在安防监控、倒车影像、图像分析、影视拍摄和投影显示等方面都具有广泛的应用前景。

参考文献

[1] 祝长锋, 肖铁军. 基于FPGA的视频图像采集系统的设计[J]. 计算机工程与设计, 2008, 29(17):4404-4407.

[2] 蔺志强, 孟令军, 彭晴晴. 基于FPGA的视频图像采集系统的设计与实现[J]. 电视技术.2011, 35(17):36-38.

[3] 董小龙, 施建华, 邵诗强. 基于FPGA的VGA接口裸眼3D显示系统设计[A]. 2012中国平板显示学术会议论文集[C]. 2012:559-562.

[4] 李克斌, 李世奇. 3D显示技术的最新研究进展[J]. 计算机工程. 2003, 29(12):3-4.

[5] 蒋艳红. 基于FPGA的VGA图象信号发生器设计. 电子测量技术. 2008, 31(3):78-81.

[6] 夏宇闻. Verilog 数字系统设计教程[M]. 北京:北京航空航天大学出版社. 2008:15-17.

显示器 滤波器 总线 LED ADC 无线电 电路 FPGA 仿真 Altera 信号发生器 电子 Verilog 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- spartan6套件试用心得报告--001(05-10)