零基础学FPGA(三)Verilog语法基基础基础(上)

时间:01-14

来源:互联网

点击:

作者:小墨同学

开学了...刚开学...小伙伴们的心情十分沉重...都在说,这上课的心情啊,堪比上坟..课表一发,这学期的课还真不少,一天到晚全是课,表示这学期又是一个具有挑战性的学期啊,新赛季新气象,让我们开始今天的学习吧!哈哈~

这几天复习了一下Verilog的语法知识,就借此写写我对这些东西的想法吧。感觉呢,是和C语言差不多,具有C语言基础的朋友学起来应该没什么问题,和C语言相同的地方就不说了吧,重点说一下不同点吧。

1、模块的结构

模块呢,是Verilog的基本设计单元,它主要是由两部分组成,一个是接口,另一个是逻辑。下面举一个小例子说明一下:

module xiaomo (a,b,c,d);

input a,b;

output c,d;

assign c=a|b;

assign d=a&b;

endmodule

所谓接口就是第二,三行,说明了一个模块的信号流向,很明显,a,b是输入,c,d是输出;第四第五行是逻辑,即输入和输出之间的关系即c的值是a或b的结果。assign 是连续赋值语句,这个以后再说。

第一行是模块的端口声明,即说明一个模块具体有那几个接口,有多少接口写多少,直接套模板就可以module(接口1,接口2……);endmodule代表此模块结束;

2、模块的内容

模块的内容包括3个部分,I/O说明,内部信号说明和功能定义。

关于I/O说明有三种格式,即输入、输出、输入输出,第三种格式代表信号可以双向传送。在写I/O说明的时候要注明信号位宽,即由几位组成,例如 input [7:0] xiaomo;代表输入一个8位的信号“小墨”,注意这里要用中括号,第一位是位宽减1,接一个冒号,再接数字0,再接端口名;

关于内部信号说明要用到和端口有关的wire和reg类型变量的声明。模板和上面类似,关于reg和wire变量后面再说。

关于功能定义是模块中最重要的部分,有三种方法可在模块中产生逻辑

(1)用assign声明语句,assign 语句主要用于组合逻辑电路

(2)用实例元件,例如 and #2 u1(q,a,b);(这个我自己概念也有点模糊,不知道怎么解释)

(3)用always块,例如 always @(clk or clr)

begin

………

end;

always语句既可以用于描述组合逻辑,也可以描述时序逻辑,但主要以描述时序逻辑电路为主。

小结

在verilog语法中,所有的过程块(包括initial块,always块),连续赋值语句,实例引用都是并行的,也就是说在一个模块中遇到这些语句就是同时执行的,而且没有先后次序。只有连续赋值语句assign和实例引用语句可以独立于过程块存在于模块的功能定义部分,即这两种语句可以不用在那两个过程块里执行,也可以在模块的功能定义部分执行,例如第一个例子。

这些和C语言有点不同,对于初学者来说应该都要弄明白。

3、数据类型、变量、常量

对于初学者来说,数据类型只要掌握好reg,wire,integer和parameter型就够了,其他类型可以暂时不用去理会。

(1)常量就不说了,比较基础。

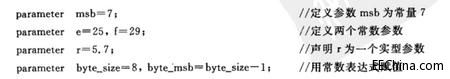

(2)参数型(parameter型)

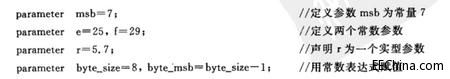

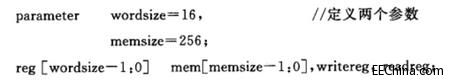

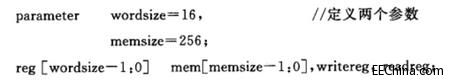

parameter是用来定义一个常量的,个人理解和C语言里面的int,float 语句一样,不一样的是parameter既可以定义整型,也可以定义浮点型或者是表达式。例如

(3)变量

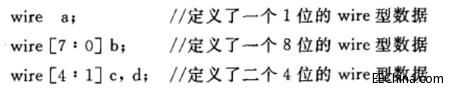

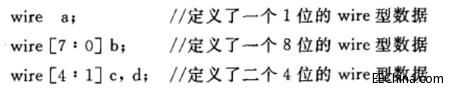

wire型数据常用来表示用以assign关键字指定的组合逻辑信号。Verilog程序模块中输入、输出信号类型默认时自动定义成wire型。例子

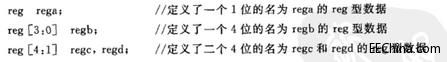

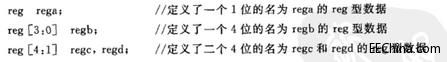

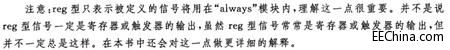

reg型数据是寄存器变量,常用来表示always块中的指定信号,常代表触发器。注意,在always块中被赋值 的每一个信号都必须定义为reg型

。

上面这句话表示不理解,求大神解释...先放这儿吧..

memory型

由于Verilog中没有多维数组的存在,memory数据就是通过扩展reg型数据的地址范围来生成的,他的格式为

reg[n-1:0] 存储器名[m-1:0];

我举个例子,比如我定义 reg[7:0] xiaomo[255:0];

这句话的意思是说,我定义了一个名叫“小墨”的存储器,这个存储器中有256个8位reg型寄存器,只要理解了这句话,就差不多了。注意,当没有中括号时代表的是一位,例如

reg xiaomo[m-1:0];代表一个名为“小墨”的存储器,里面有m个1位的reg型寄存器。

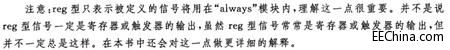

还有个地方我感觉不太明白,见下图,谁知道这句话上面意思...求大神解释...

下面这几句话需要注意

4、运算符及表达式

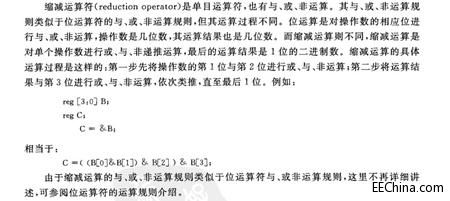

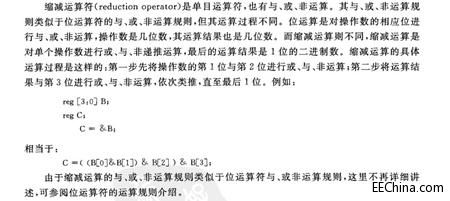

这里和C语言几乎一样,就不做过多解释了吧。就说一下位拼接运算符和位减运算符,这里C语言里面没有。

直接看个例子就可以

5、赋值语句

赋值语句共有两种,即非阻塞赋值,和阻塞赋值。

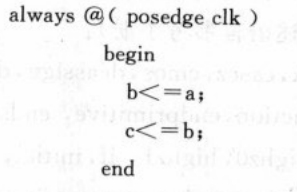

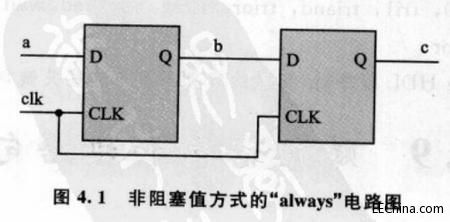

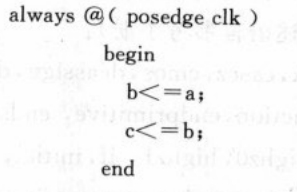

(1)非阻塞赋值

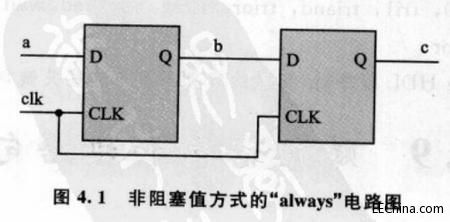

非阻塞赋值方式所赋值的变量不能立即就为下面语句所用,只有当块结束后才能得到上一次所附的值,这种赋值方式是编写可综合的时序逻辑时常用的赋值方式。例如

这个例子的意思是,当时钟上升沿到来时,a的值给b,b的值给c,但是只有当块结束时才完成赋值,这么说吧,假如原来a=1,b=2那么当时钟上升沿到来时a=1,b=2,c=2;当块结束时,a=b=c=1;

这么理解对吗?求大神指点...

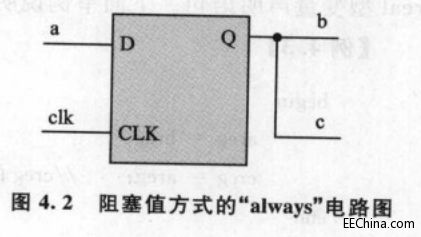

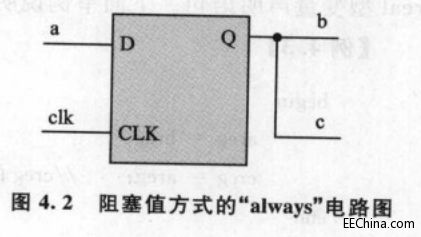

(2)阻塞赋值

与非阻塞赋值不同,赋值语句执行完后块才结束,b 的值在赋值语句结束后立刻改变,但是在时序逻辑电路中可能会出问题。

always @(clk or clr);

begin

b=a;

c=b;

end

假如开始a=1;当当时钟上升沿到来时,a=b=c=1;然后块结束

开学了...刚开学...小伙伴们的心情十分沉重...都在说,这上课的心情啊,堪比上坟..课表一发,这学期的课还真不少,一天到晚全是课,表示这学期又是一个具有挑战性的学期啊,新赛季新气象,让我们开始今天的学习吧!哈哈~

这几天复习了一下Verilog的语法知识,就借此写写我对这些东西的想法吧。感觉呢,是和C语言差不多,具有C语言基础的朋友学起来应该没什么问题,和C语言相同的地方就不说了吧,重点说一下不同点吧。

1、模块的结构

模块呢,是Verilog的基本设计单元,它主要是由两部分组成,一个是接口,另一个是逻辑。下面举一个小例子说明一下:

module xiaomo (a,b,c,d);

input a,b;

output c,d;

assign c=a|b;

assign d=a&b;

endmodule

所谓接口就是第二,三行,说明了一个模块的信号流向,很明显,a,b是输入,c,d是输出;第四第五行是逻辑,即输入和输出之间的关系即c的值是a或b的结果。assign 是连续赋值语句,这个以后再说。

第一行是模块的端口声明,即说明一个模块具体有那几个接口,有多少接口写多少,直接套模板就可以module(接口1,接口2……);endmodule代表此模块结束;

2、模块的内容

模块的内容包括3个部分,I/O说明,内部信号说明和功能定义。

关于I/O说明有三种格式,即输入、输出、输入输出,第三种格式代表信号可以双向传送。在写I/O说明的时候要注明信号位宽,即由几位组成,例如 input [7:0] xiaomo;代表输入一个8位的信号“小墨”,注意这里要用中括号,第一位是位宽减1,接一个冒号,再接数字0,再接端口名;

关于内部信号说明要用到和端口有关的wire和reg类型变量的声明。模板和上面类似,关于reg和wire变量后面再说。

关于功能定义是模块中最重要的部分,有三种方法可在模块中产生逻辑

(1)用assign声明语句,assign 语句主要用于组合逻辑电路

(2)用实例元件,例如 and #2 u1(q,a,b);(这个我自己概念也有点模糊,不知道怎么解释)

(3)用always块,例如 always @(clk or clr)

begin

………

end;

always语句既可以用于描述组合逻辑,也可以描述时序逻辑,但主要以描述时序逻辑电路为主。

小结

在verilog语法中,所有的过程块(包括initial块,always块),连续赋值语句,实例引用都是并行的,也就是说在一个模块中遇到这些语句就是同时执行的,而且没有先后次序。只有连续赋值语句assign和实例引用语句可以独立于过程块存在于模块的功能定义部分,即这两种语句可以不用在那两个过程块里执行,也可以在模块的功能定义部分执行,例如第一个例子。

这些和C语言有点不同,对于初学者来说应该都要弄明白。

3、数据类型、变量、常量

对于初学者来说,数据类型只要掌握好reg,wire,integer和parameter型就够了,其他类型可以暂时不用去理会。

(1)常量就不说了,比较基础。

(2)参数型(parameter型)

parameter是用来定义一个常量的,个人理解和C语言里面的int,float 语句一样,不一样的是parameter既可以定义整型,也可以定义浮点型或者是表达式。例如

(3)变量

wire型数据常用来表示用以assign关键字指定的组合逻辑信号。Verilog程序模块中输入、输出信号类型默认时自动定义成wire型。例子

reg型数据是寄存器变量,常用来表示always块中的指定信号,常代表触发器。注意,在always块中被赋值 的每一个信号都必须定义为reg型

。

上面这句话表示不理解,求大神解释...先放这儿吧..

memory型

由于Verilog中没有多维数组的存在,memory数据就是通过扩展reg型数据的地址范围来生成的,他的格式为

reg[n-1:0] 存储器名[m-1:0];

我举个例子,比如我定义 reg[7:0] xiaomo[255:0];

这句话的意思是说,我定义了一个名叫“小墨”的存储器,这个存储器中有256个8位reg型寄存器,只要理解了这句话,就差不多了。注意,当没有中括号时代表的是一位,例如

reg xiaomo[m-1:0];代表一个名为“小墨”的存储器,里面有m个1位的reg型寄存器。

还有个地方我感觉不太明白,见下图,谁知道这句话上面意思...求大神解释...

下面这几句话需要注意

4、运算符及表达式

这里和C语言几乎一样,就不做过多解释了吧。就说一下位拼接运算符和位减运算符,这里C语言里面没有。

直接看个例子就可以

5、赋值语句

赋值语句共有两种,即非阻塞赋值,和阻塞赋值。

(1)非阻塞赋值

非阻塞赋值方式所赋值的变量不能立即就为下面语句所用,只有当块结束后才能得到上一次所附的值,这种赋值方式是编写可综合的时序逻辑时常用的赋值方式。例如

这个例子的意思是,当时钟上升沿到来时,a的值给b,b的值给c,但是只有当块结束时才完成赋值,这么说吧,假如原来a=1,b=2那么当时钟上升沿到来时a=1,b=2,c=2;当块结束时,a=b=c=1;

这么理解对吗?求大神指点...

(2)阻塞赋值

与非阻塞赋值不同,赋值语句执行完后块才结束,b 的值在赋值语句结束后立刻改变,但是在时序逻辑电路中可能会出问题。

always @(clk or clr);

begin

b=a;

c=b;

end

假如开始a=1;当当时钟上升沿到来时,a=b=c=1;然后块结束

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)